## An Integrated Functional Solution for Multi-core Programming on The Cell Broadband Engine

Nathaniel Azuelos

Department of Electrical & Computer Engineering McGill University Montreal, Canada

January 2009

A thesis submitted to McGill University in partial fulfillment of the requirements for the degree of Master of Engineering.

© 2009 Nathaniel Azuelos

### Abstract

Recent efforts in microprocessor development tend to the coexistence of several Central Processing Units(CPUs) on a single chip. The Cell Broadband Engine (CBE), the fruit of collaboration between Sony, Toshiba and IBM, integrates IBM's legacy PowerPC CPU with a new set of simple cores, all of which communicate through a high speed bus. The multiple cores on the CBE allow users to exploit the parallel nature of their programs. However, it is often difficult to efficiently extract the parallelism from an application and to distribute tasks in a suitable fashion. We propose a dataflow approach to CBE computing where the compiler is in charge of task partitioning and of the infrastructure for runtime distribution of tasks.

In this work, we present the NCC programming language, Squid compiler and runtime environment. NCC is a strict functional dataflow language that forces explicit variable dependencies, in order to exploit parallelism in the application. NCC code is thus written by the user without specifying parallelism explicitly. The Squid Compiler draws a virtual data flow graph from the NCC source. This graph is then partitionned according to implementationspecific criteria into tasks and supertasks. The individual tasks are then translated to ANSI C, and supertasks are analyzed and transformed into scheduling structures. All tasks are executed by the CBE's simple cores. The Squid Runtime Environment (SRE) interacts with the generated scheduler to order tasks' execution, running the supertasks' scheduling, and managing garbage collection. The SRE runs on the CBE's PowerPC core as a separate thread to implement a host-device paradigm, and as resident code on the simple cores.

## Résumé

Les récents efforts en développement de microprocesseurs tendent à une coexistence entre plusieurs Unités Centrales (UC) sur une seule puce. Le Cell Broadband Engine (CBE), le fruit d'une collaboration entre Sony, Toshiba et IBM, intègre le CU patrimonial d'IBM PowerPC avec un nouvel ensemble d'unités simples, communiquant entre elles avec un bus de haute vitesse. Les nombreueses unités présentes dans le CBE permettent aux utilisateurs d'exploiter la nature parallèle de leurs programmes. Cependant, il est souvent difficile d'extraire le parallelisme d'une application et de distribuer des tâches de façon appropriée. Nous proposons donc d'approcher la programmation du CBE sous une perspective de flux de données où le compilateur est chargé de partitionner les tâches et de l'infrastructure de la distribution dynamique des tâches.

Dans ce travail, nous présentons la langue de programmation NCC, le compilateur et l'environnement d'exécution Squid. NCC est un langage fonctionnel stricte de flux, qui force les dépendances entre variables à être explicites, afin d'exploiter le parallelisme d'une application. Le code NCC est donc rédigé par l'utilsateur sans spécifier le parallelisme explicitement. Le compilateur Squid dessine un graphe de flux de données virtuel issu du code NCC. Ce graphe est alors partitionné selon des critères particuliers à l'implémentation en tâches et supertâches. Chaque tâche est ensuite traduite en ANSI-C, et les supertâches sont analysées et transformées en structures d'ordonnançement. Toutes les tâches sont exécutées par les untiés simples du CBE. L'Environnement d'Exécution Squid (EES) interagit avec l'ordonnanceur généré pour ordonner l'exécution des tâches, commander l'ordonnancemenet des supertâches, et gérer la collection de poubelle. Le EES roule sur l'untié PowerPC du CBE en tant que fil d'éxécution séparé afin d'implémenter un paradigme hôte-dispositif, et de code résident sur les untités simples.

### Acknowledgements

I would like to thank my supervisors, Profs. Zilic and Gross, for giving me the opportunity to study this fascinating field, for their advice, insight, and numerous comments in the writing of this thesis. I especially want to thank Bojan Mihajlovic for his friendship, and for always being there to answer questions; an incredible help without which this work would have never come to fruition. David Becerra for the close collaboration and friendly rivalry. Further thanks to the "elders", Jean-Samuel Chenard, Stephan Bourduas, Marc Boule, Atanu Chattopadhyay and Henry Chan for being such towering figures and true role models. A special thanks to the 4th, 5th and 6th floors for making lab life so enjoyable. Ashraf Haddad for our late night musings about politics and religion, as well as to all the other musers: Carmen, Marwan, Dani, Sadok, Mike, Francois and Euisoo. A personal thanks to my parents for their love and for the education they gave me, with its enormous emphasis on academic excellence. To my brother Ilan for his complicity and for always pushing me to sharpen my mind. To Olivier Rubel and David Tellouk for their friendships and laughs.

> רבי אלעזר בן עזריה אומר, כל שחכמתו מרובה ממששיו, למה הוא דומה-לאילן שעפיו מרובין ושורשיו מועטין, והרוח באה ועוקרתו והופכת על פניו. וכל שמששיו מרובין מחכמתו, למה הוא דומה-לאילן שעפיו מועטין ושורשיו מרובין: אפילו כל הרוחות שבעולס באות ונושבות בו, אין מזיזות אותו ממקומו (Talmud Avot 3, 21)

## Contents

| 1        | Bac | kground: Multi-Core Architectures and the Cell Broadband Engine                                            | 11        |

|----------|-----|------------------------------------------------------------------------------------------------------------|-----------|

|          | 1.1 | Multicore Architectures                                                                                    | 13        |

|          | 1.2 | CBE Architecture                                                                                           | 15        |

|          |     | 1.2.1 The PPU                                                                                              | 16        |

|          |     | 1.2.2 The SPUs                                                                                             | 17        |

|          |     | 1.2.3 Communication                                                                                        | 17        |

|          | 1.3 | Using MFC Facilities                                                                                       | 19        |

|          | 1.4 | Multiple Buffering                                                                                         | 20        |

|          | 1.5 | Programming for the CBE                                                                                    | 22        |

|          |     | 1.5.1 Scheduling $\ldots$ | 23        |

| <b>2</b> | Par | allel Programming and Functional Languages                                                                 | <b>24</b> |

|          | 2.1 | Parallel Programming Design                                                                                | 25        |

|          | 2.2 | Task Partitioning                                                                                          | 26        |

|          | 2.3 | Functional languages                                                                                       | 30        |

|          | 2.4 | Implementation of Functional Languages                                                                     | 31        |

|          | 2.5 | Future of Parallel Programming                                                                             | 33        |

|   |     | 2.5.1              | The Berkeley Conclusions               | 33 |

|---|-----|--------------------|----------------------------------------|----|

|   | 2.6 | Emerg              | ing Languages and Platforms            | 34 |

|   | 2.7 | Squid <sub>/</sub> | SRE: an integrated three-step solution | 36 |

|   |     | 2.7.1              | Why NCC/Squid/SRE                      | 38 |

| 3 | NC  | C/Squ              | id                                     | 39 |

|   | 3.1 | Design             | of a Dataflow Language                 | 39 |

|   |     | 3.1.1              | Variables, Data Types and Syntax       | 40 |

|   |     | 3.1.2              | Scopes                                 | 41 |

|   | 3.2 | NCC o              | constructs                             | 43 |

|   |     | 3.2.1              | Scalars and Arrays                     | 44 |

|   |     | 3.2.2              | Basic Expressions                      | 46 |

|   |     | 3.2.3              | Loops                                  | 46 |

|   |     | 3.2.4              | Functions                              | 49 |

|   | 3.3 | Block              | Partitioning                           | 50 |

|   |     | 3.3.1              | Decisions                              | 50 |

|   |     | 3.3.2              | Multilevel Graph Partitioning          | 52 |

|   |     | 3.3.3              | Array Quantization                     | 55 |

|   | 3.4 | Future             | e Work                                 | 58 |

| 4 | The | squid              | Runtime Environment                    | 60 |

|   | 4.1 | Pease              | FFT in NCC/Squid                       | 62 |

|   | 4.2 | Anato              | my of the SRE                          | 66 |

|          | 4.3           | SPU a  | natomy                                     | 67 |

|----------|---------------|--------|--------------------------------------------|----|

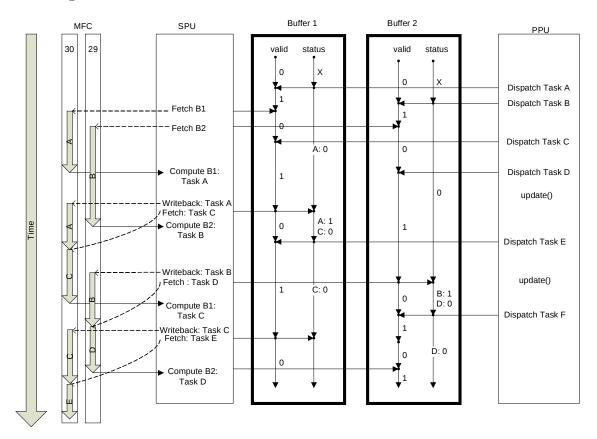

|          |               | 4.3.1  | Multiple Buffering                         | 67 |

|          |               | 4.3.2  | Functions                                  | 69 |

|          |               | 4.3.3  | The Buffer                                 | 69 |

|          |               | 4.3.4  | Multiple Buffering Control                 | 71 |

|          | 4.4           | PPU a  | anatomy                                    | 73 |

|          |               | 4.4.1  | Dispatch Table                             | 73 |

|          |               | 4.4.2  | The Task List                              | 74 |

|          |               | 4.4.3  | Supertask list                             | 74 |

|          |               | 4.4.4  | The Task Object                            | 75 |

|          |               | 4.4.5  | The Supertask Object                       | 77 |

|          |               | 4.4.6  | The Data Object                            | 78 |

|          | 4.5           | Mecha  | nics of the SRE                            | 79 |

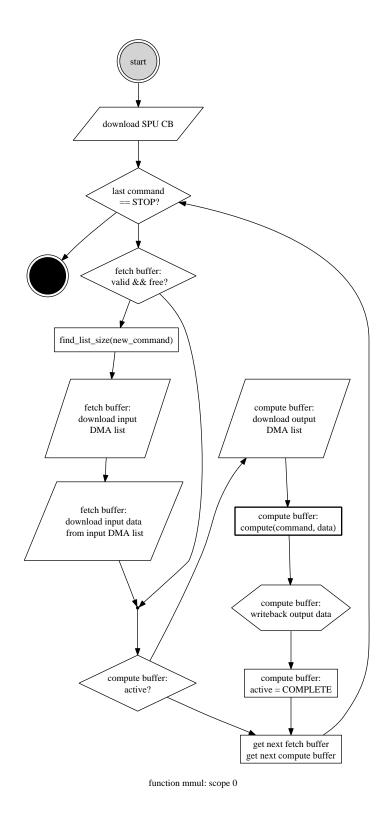

|          |               | 4.5.1  | SPU SRE                                    | 79 |

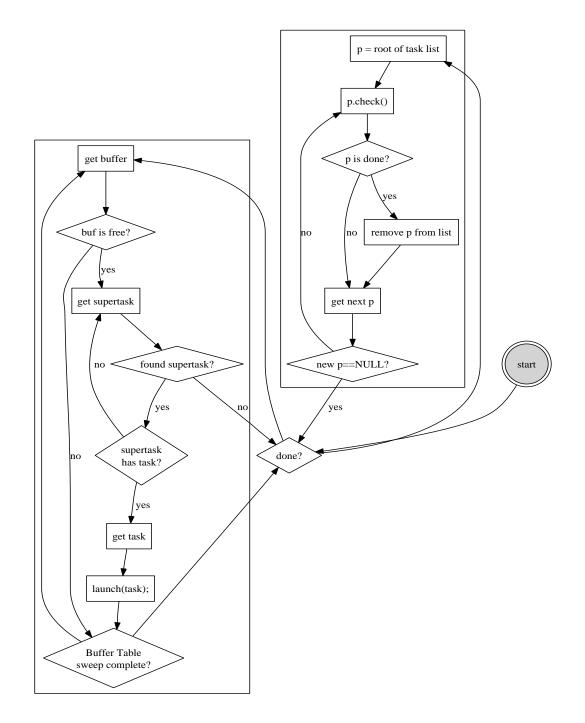

|          |               | 4.5.2  | PPU SRE                                    | 82 |

|          |               | 4.5.3  | Coordinating Between the PPU and SPU SRE's | 85 |

|          | 4.6           | Simple | e Results                                  | 86 |

|          | 4.7           | Future | e Work                                     | 87 |

| <b>5</b> | Con           | clusio | n                                          | 88 |

| Re       | References 89 |        |                                            |    |

|          |               |        |                                            | 55 |

## List of Figures

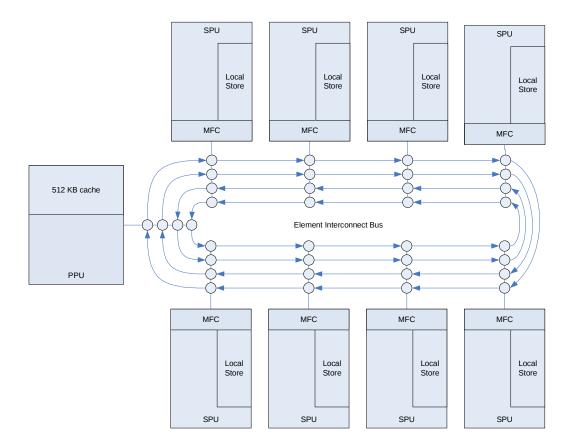

| 1.1 | A top-level view of the Cell Broadband Engine                                | 16 |

|-----|------------------------------------------------------------------------------|----|

| 1.2 | Double buffering using tag groups                                            | 21 |

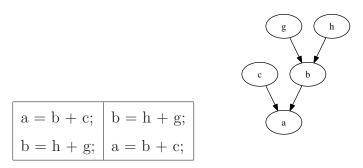

| 3.1 | Inverting the order of statements does not change the DAG                    | 43 |

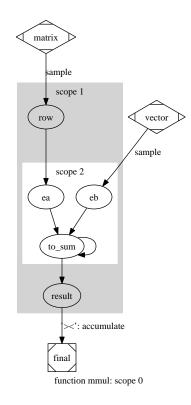

| 3.2 | Matrix-vector multiplication expressed in NCC.                               | 43 |

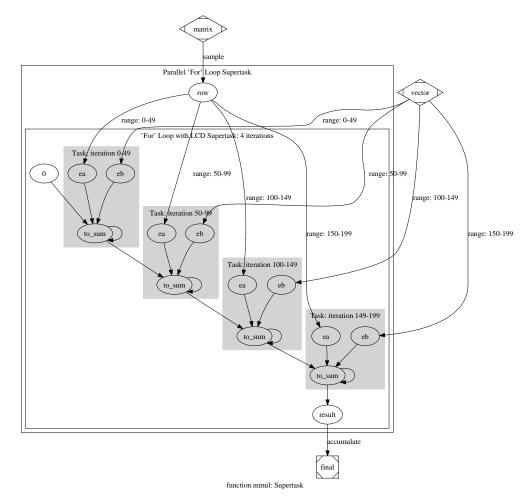

| 3.3 | Equivalent DAG of the code in Figure 3.2                                     | 44 |

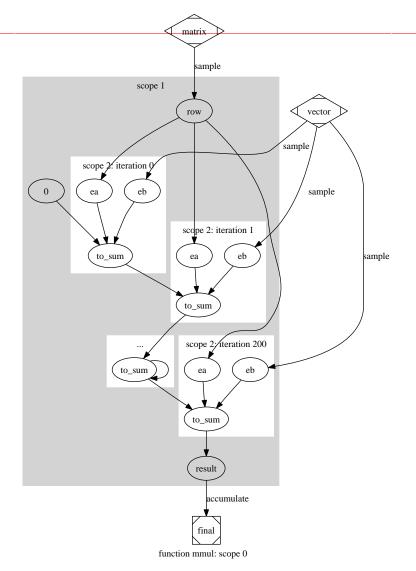

| 3.4 | Matrix vector multiplication example with unrolled inner loop                | 48 |

| 3.5 | Matrix vector multiplication example with partitioned inner loop             | 54 |

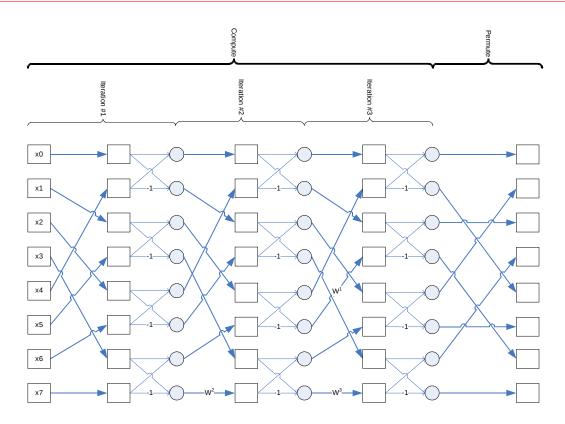

| 4.1 | Dataflow of an 8-point Pease FFT                                             | 64 |

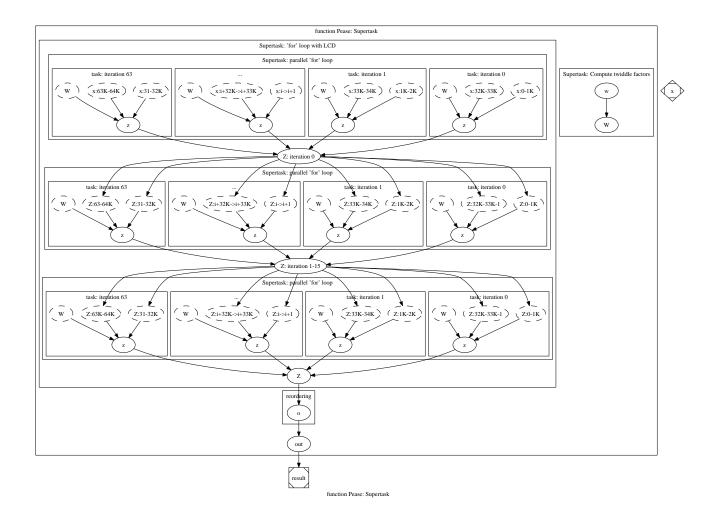

| 4.2 | The Pease FFT algorithm divided by Squid                                     | 65 |

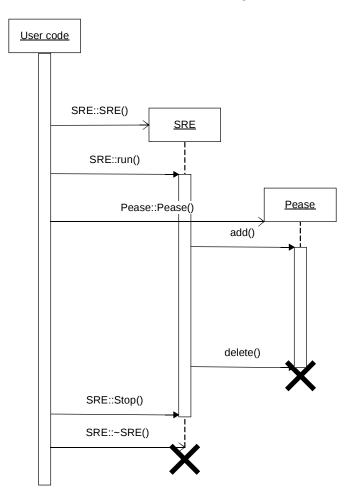

| 4.3 | UML sequence diagram of the execution of the Pease() function under the SRE. | 66 |

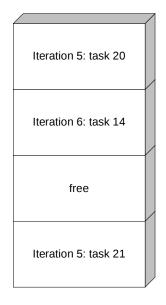

| 4.4 | An example state of 4 buffers running the Pease FFT example                  | 68 |

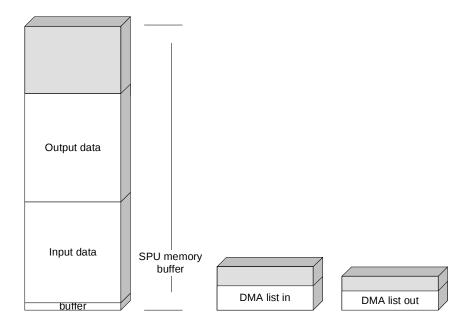

| 4.5 | The memory structures to hold task buffering information                     | 72 |

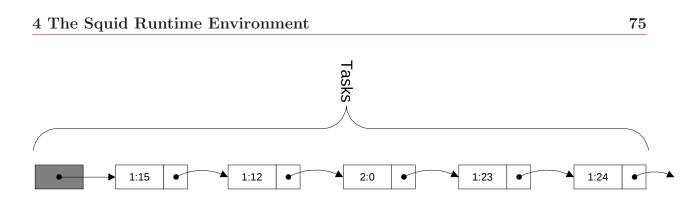

| 4.6 | The Task List                                                                | 75 |

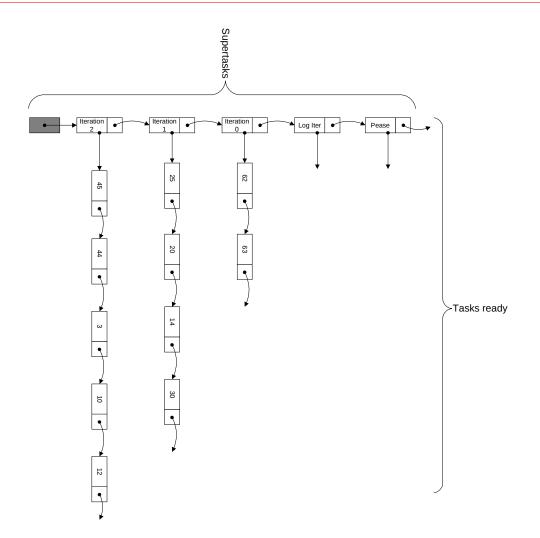

| 4.7 | The Supertask List                                                           | 76 |

| 4.8 | Flow chart of the operation of the SPU SRE                                   | 80 |

| 4.9  | High-level flowchart of PPU SRE execution                              | 83 |

|------|------------------------------------------------------------------------|----|

| 4.10 | Coordinating through the MFC between the PPU SRE and the SPU SRE. $$ . | 85 |

## List of Tables

| 4.1 | A half active 3-SPU table with 2 buffers per SPU | 74 |

|-----|--------------------------------------------------|----|

| 4.2 | Timing results                                   | 86 |

### Chapter 1

## Background: Multi-Core Architectures and the Cell Broadband Engine

The exponential growth in transistor density dictated by Moore's Law has been the primary source of increase in computing power in microprocessors since their inception. Microprocessors accelerated applications by exploiting instruction level parallelism present both statically and dynamically through advanced techniques and analysis, by compilers on the one hand, and intelligent architectures on the other. As integrated circuits further grew in size, an increasing proportion of their area was dedicated to multi-level caches in order to confront the high memory bandwidth consumed by data-intensive applications. These techniques were quickly subject to the law of diminishing returns. As transistor density further increases, multi-core processors quickly became an interesting alternative.

Contrary to on-chip multi-core processors, multi-chip multiprocessor systems have existed for a long time and were thouroughly studied. In most cases, the differences between implementations of multiprocessors lay in the method of communication and memory coherence. Intuitively, the problems and solutions developed for multiprocessor systems would apply as well to multi-core systems. From a high-level perspective, the solutions proposed were indeed similar. However, the physical proximity of the cores has led to subtle and interesting differences with traditional multiprocessor implementations. The communication latencies are drastically shorter, and cores may share caches and random access memory. The Cell Broadband Engine (CBE) is IBM's solution to the multi-core challenge. It consists of a heterogeneous mix of its legacy PowerPC CPU (PPU) and a varying number of Synergistic Processing Units (SPUs). It is generally considered one of the most computationally powerful CPUs on the market [1].

The long-awaited arrival of multi-core CPUs had an important impact on software development. Until recently, parallel programming was the domain of experts and the concern of a select few. With the advent of multi-core CPUs, software developers now need to consider parallel implementation of their code in order to increase performance for the common machine. Unfortunately, there are great difficulties in parallel software development, such as synchronization, code and data partitioning, and subtle hazards that may occur. In most cases, the parallel portions of an application are explicitly specified and synchronization methods have paramount importance. Further, intimate knowledge of the multiprocessor architecture at hand is necessary.

High-level design principles of multiprocessors have provided a basis to the hardware implementation of multi-core CPUs. Similarly, software paradigms applicable to the former were applied to the latter. Unfortunately, the difficulties of parallel programming for multiprocessors have also been inherited. However, the ubiquity of parallel systems propagated these difficulties to a much larger spectrum of programmers. Fortunately, alternative software paradigms developed for multiprocessors still apply in the multi-core era, and are well worth being revisited.

One such alternative solution is the fruit of a long history of research into programming languages. *Functional programming languages* describe the computations rather than dictate their order. The order of computation can be deduced from an analysis of the data dependencies between computation quanta. Further, parallel threads of computation become evident and can be scheduled to be performed simultaneously.

The order in which parallel threads extracted from functional code are executed can be

better determined at runtime. It is extremely difficult for a compiler, and even more so for a programmer, to predict accurately the resource usage of an application at a given moment. Therefore, such work is best left to a *runtime environment*. This approach to functional programming is called *lazy*, as data is computed only once it is needed. There is a number of lazy programming languages, the most popular of which is Haskell. A large body of work has been produced on the subject of the implementation of lazy programming languages on multiprocessors.

This thesis suggests a three-step solution to the challenge of multi-core programming. The CBE is chosen as a target for this implementation as it is easily available and a good example of future CPUs. A functional programming language bearing much resemblance to C is described. Its compilation is then documented. Finally, the anatomy and mechanics of the runtime environment in charge of distributing computation are elaborated. However, an overview of multi-core architectures, parallel programming, current solutions, as well as the motivations for our work are first offered.

#### **1.1 Multicore Architectures**

The recent migration from uniprocessors to the multi-core era stems from the realization that uniprocessor development has reached fundamental limits. The three major concerns in the development of new architectures have been identified for some time, and are known as the three "walls". The first and foremost is the "Power Wall": increasing clock frequency, transistor count and die size increases power consumption density at an unsustainable rate. Serious considerations must be taken to reduce power density. Further, the increase in the size of silicon dies causes the distance to outside interfaces to increase and is designated as the "Memory Wall". The access time for memory loads and stores to Dynamic Random Access Memory (DRAM) is now attaining hundreds of clock cycles. The final challenge is related to the amount of instruction level parallelism (ILP), the "ILP Wall". Dedicating an increasing amount of resources to exploit parallelism between low-level instructions faces the law of diminishing returns.

Despite these drawbacks, Moore's law still applies to the size of integrated circuits. The large amount of die size available brings about new possibilities to tackle these problems. First, the more cores lay on a chip, the higher the theoretical maximal computing power. However, deciding the size and functionality of these cores is quite important. With its dual and quadcore processors, Intel has for now chosen the simplest way: replicating complex cores on a single die that share cache resources. It seems however that this approach is temporary and Intel has already created a prototype [2] with 80 simple cores on a single chip.

The use of simple cores has been subject of some study [3], and is proving popular. The CBE currently includes up to 8 simple Single Instruction Multiple Data (SIMD) cores on a single chip. Graphical Processing Units (GPUs) have integrated a large amount of cores for quite some time, and NVIDIA has recently provided application programming interfaces (APIs) to adapt their GPUs to general purpose computing. Sun's Niagara [4] T1 and T2 processors also consist of 8 cores with multi-threading capability and shared L2 cache. The popularity of the simple core approach is due to the following considerations [5]:

- 1. Power: eliminating ILP-exploiting units to the benefit of extra cores leads to a net benefit in computing power per Watt [6].

- 2. Cost: the cost of large chips is amortized by the increased computing power of new cores.

- 3. Defect Tolerance: among a large number of cores, the loss of a few to silicon defects does not void the usability of a chip. Sun and IBM deliver chips with some cores turned off to increase die yield in the Niagara and CBE respectively.

Kumar *et. al* [7] however argue in favor of the benefits of a heterogeneous architecture, where cores with different capabilities reside on the same chip. They propose to maintain at least one core to efficiently run scalar sequential code. Using this model, they achieve an increase in performance of up to 63%. Such a result is a consequence of Amdahl's law [8] that finds

the effect of the sequential portion of a code in a parallel environment as an asymptotic limiting factor. The issue of homogeneous v.s. heterogeneous multiprocessor architectures was studied by Andrews [9]. It led to simulations for multi-core systems by Becchi [10] and Sondag [11] that show that significant runtime performance can be exploited from a dynamic profiling of threads during execution in heterogeneous systems.

#### **1.2 CBE Architecture**

The Cell Broadband Engine (CBE) [12] is IBM and Sony's solution to the multi-core challenge. The CBE was initially distributed at very low cost (\$400) on Sony's Playstation 3 gaming platform, and is now an integral part of the US Department of Energy Road Runner super-computer project that claims to have achieved the elusive PetaFLOP. The work presented in this thesis attempts to present an integrated solution to the goal of a new and efficient platform to multi-core programming. We focus our work on an implementation for the CBE, due in part to its popularity, but mostly because we believe it provides a realistic preview of technologies to come.

The power of the CBE does not rest solely on the number of its cores (7-9 on current platforms). It incorporates a single unit of IBM's legacy PowerPC computing core (PPU) with vector extensions and 512KB of cache. Its other cores are SIMD cores with 128-bit register files designated as Synergistic Processing Units (SPUs). These are "stripped": no hardware units are included to perform out-of-order instruction execution, predictive branching and other such ILP-exploiting features. Finally, its Element Interconnect Bus (EIB), a 4ring packet network, allows extremely fast communication between cores and with external interfaces. Figure 1.1 shows a top-level view of the CBE.

In opposition to the PPU and most other cores in different architectures, the SPU does not have a cache. It accesses a small 256KB *local store* that allows very fast local memory access and is **not** coherent to Main Memory. To access Main Memory, Direct Memory Access (DMA) commands are provided. The CBE is not designed as a strictly distributed memory

Fig. 1.1: A top-level view of the Cell Broadband Engine

machine however; every local store is mapped to locations in the global virtual memory. The CBE designers thus allowed programmers to use both message-passing and shared memory approaches.

#### 1.2.1 The PPU

The PPU implements exactly the PowerPC standard, version 2.02 [13]. Its virtual memory is designed for 64-bit addressing, although it still supports 32-bit addressing for backward compatibility. In fact, it is sometimes preferable to use 32-bit addressing, when atomic or mailbox messages (described below) of memory addresses are involved. The PPU's VMX extension offers it SIMD capability, although its smaller register size does not allow it to match the computational power of the SPUs.

#### 1.2.2 The SPUs

The SPU architecture is that of a simple two pipeline SIMD processor. The simplicity of the design causes many low-level code generation considerations. First, the two pipeline design allows the simultaneous execution of two instructions. The first pipeline is dedicated to arithmetic operations, whereas the second to memory accesses and shuffle instructions. The second, more significant, consideration is the fully SIMD nature of the processor. Contrary to the PPU, the instruction set of which is augmented by SIMD capabilities, the SPU architecture *only* performs SIMD instructions. In particular, all memory accesses are aligned on a 16-byte boundary. Consequently, to execute scalar code, re-alignment operations are very often needed, particularly when accessing array elements. Scalar code is thus very costly in SPU performance.

Whereas scalar code is very inefficient on the SPU, parallel code is very efficiently processed. The 16-byte registers allow 16 simultaneous operations for char data types, 8 for short, 4 for int and float. This capability allows acceleration by a significant factor, although the inevitability of scalar code usually hinders performance.

The small amount of memory in local store is an important limiting factor when using SPUs. The local store must hold stack, heap, and code at runtime, and the optimization of the space used is a challenging problem. Specifically, this problem can be limiting in the amount of code available. Libraries can be quite large, and space devoted to code grows too quickly with respect to the space left for processing data. *Code overlay* is an important technique in SPU programming: dedicated regions of memory are reserved for a group of code elements. Code elements can be swapped so only one of a group may be resident on the local store at any time, significantly saving space and extending SPU capability.

#### 1.2.3 Communication

The EIB [14] can reach a theoretical bandwidth of over 300 GB/s, although practically, only about 200GB/s is realizable. The ring network transfers packets in sizes of 16 bytes. As a

result, data transfer sizes must be multiples of 16 bytes, although one, two, four and eight byte packets may be sent. Further, when accessing memory outside local stores, a data alignment of 128 bytes is required of the hardware. This requirement is due to the fact that the PPU cache performs snooping on bus addresses. Since cache lines are 128 bytes wide, the memory addresses snooped must be so aligned. In order to initiate transfers to and from SPEs, it accesses the target SPE's Memory Flow Controller (MFC) through its address in the global virtual memory. These memory transfers are dubbed *proxy DMA* commands, and are handled slightly differently than SPU-initiated transfers. To every core is attached a Memory Flow Controller (MFC) to interface access to the bus. The MFC can read and write to the local store, as well as perform atomic operations. All instructions used by SPUs to send commands to the MFC run through the SPU's memory pipeline. Communication with the MFC is done through the following channels:

- SPU event channels, to control the response to external events

- SPU signal notification channels, used by MFCs to send 32-bit messages to one another

- SPU decrementer channels, for timing purposes

- MFC multisource synchronization channels, to enforce barriers in communication

- SPU and MFC read mask channels, to access specific elements of MFC and SPU control registers

- SPU state management channels, used by the Operating System

- MFC command channels, to initiate, coordinate and act upon data transfers

- MFC tag status channels, to identify the status of specific transfers

- MFC mailbox channels, that offer a more elaborate short message communication mechanism

These facilities provide the MFC an array of mechanisms, some simple and others complex, to communicate with other MFCs. However, most of these are too complex to be used by the common user or a robust runtime environment. Of particular interest to the application developer are the following: DMA transfers, atomic operations, and mailbox communication.

#### 1.3 Using MFC Facilities

DMA transfers, as previously stated, are guaranteed to be memory coherent: data in main memory, PPU cache and data being distributed through the MFC, are identical for a given memory address. Hence, simultaneous operations on memory locations will not occur. In order to optimize the use of the EIB, the MFC may reorder memory transfers, and the commands sent to the MFC, although coherent, may cause data hazards with respect to the application's purpose. Further, in order to avoid long delays due to data transfers, the SPU overlaps data transfer and execution. Synchronization mechanisms are thus required to ensure program correctness. Tag group status registers, *fences* and *barriers* are such mechanisms.

Tag Groups are particularly useful in CBE programming. At several moments during an application lifetime arises the need to synchronize execution and the completion of a data transfer. Further, several DMA transfers may be active simultaneously, and there might be a need to synchronize on one's completion rather than every single one. To that effect, to every DMA transfer is associated a tag group identification, ranging from 0 to 31. This identification mechanism allows developers to synchronize multiple DMA commands with the same tag, independently of all others. Tag mask registers are present to specify, upon synchronization, which groups status must be checked.

Fences and barriers offer synchronization between data transfers rather than with program execution. A fenced MFC command forces the MFC to perform the data transfer only once all previously issued commands with the same tag group have completed. Barrier commands force all previously issued commands, no matter what their tag group, to not follow it, and no command issued thereafter may precede it.

Another important tool made available by the architecture is the *DMA list*. The DMA list is the CBE's tool to perform *gather* operations; data scattered in memory is collected in a continuous block of memory. It offers software the possibility of avoiding the specification of a single source, single destination for every DMA transfer. A single DMA command is issued, where a list of transfers is sent to the MFC. Every transfer is identified by its size and source address. A single destination is specified, to which all transfers will accumulate. DMA lists thus allow an efficient way of performing several transfers at once. It is interesting to note that there is no equivalent *scatter* command made available by the architecture.

Beyond DMA transfers, atomic operations allow simple and efficient coherent arithmetic and memory access to memory, whether local or foreign. A very small atomic command cache makes their use particularly attractive for synchronization purposes. Mailbox messages are well suited to that purpose as well. They are not used in this work however, and we shall thus refrain from elaborating on their details.

#### 1.4 Multiple Buffering

Tag groups enables the use of a very important technique in CBE programming: *multiple buffering*. It is used generally in the context of large independent parallel loops, where the data access pattern is well determined in advance. A fixed, limited number of input and output buffers are created in SPU local store to overlap one loop's data transfers and the next's communication. By using different tag groups, synchronization may be performed on one iteration's fetch while another's continues still. Meanwhile, one output buffer's writeback and another input buffer's fetch may be assigned the same tag group, in order to validate the execution of an iteration dedicated to these buffers. The following code offers a double buffering example, and is represented in Figure 1.2:

//create 2 input and output buffers

float input\_buf[2][256];

float output\_buf[2][128];

```

int mm_address_in = ...;

int mm_address_out = ...;

mfc_get(input_buf[0], mm_adress_in, 0); //initiate first transfer

int i;

for(i=0; i<C; i+=2){</pre>

mm_address_in += 256;

mfc_get(input_buf[1], mm_adress_in, 1); // get next data for buffer 1

// ensure last get and put are complete

sync_tag(0);

// compute on buffers 0

mfc_put(input_buf[0], mm_address_out, 0); // write back buffer 0 result

mm_address_out += 128;

mm_address_in += 256;

mfc_get(input_buf[0], mm_address_in, 0); // get next data for buffer 0

// ensure last get and put are complete

sync_tag(1);

//compute on buffers 1

mfc_put(input_buf[1], mm_address_out, 1); // write back buffer 1 result

mm_address_out += 128;

}

. . .

Tag

#0

fetch

Compute

put

get

Compute

put

Тад

fetch

Compute

put

Compute

#1

Time

```

Fig. 1.2: Double buffering using tag groups

#### 1.5 Programming for the CBE

The heterogeneity of the CBE's cores and the multiple details in its inter-core communication mechanisms add further complexity to the parallel programming problems described previously [15]. The CBE Programming Tutorial [16] and Handbook [17] offer several programming techniques and some others have been offered by the literature [18, 19]. DeKruijf proposes the use of Google's MapReduce algorithm to transparently distribute tasks to SPUs.

As it stands, gcc implements several optimization techniques, notably auto-SIMD-ization of SPU code. A powerful SDK including a full-system simulator, as well as a runtime API are provided by IBM/Sony. A set of macro commands are available in the API to simplify channel writing to the MFC [20]. Unfortunately, gcc does not perform code partitioning or implement multiple buffering techniques. Beyond gcc, several solutions have been developed to simplify code generation for the CBE. These usually follow the traditional parallel programming approaches, as both MPI [21] and OpenMP [19, 22] tools are available, the latter as part of IBM's XL compiler suite. An implementation of the Java Virtual Machine has also been developed as an academic project [23].

IBM's Accelerated Library Framework (ALF) [24] offers programmers an integrated environment to partition computational kernels written by the user. Divided tasks, or *work blocks*, are dynamically distributed by a runtime environment to which the main threads passes tasks to accelerate. However, it does not do so from a simple source code, and kernels must be defined as such by the user. To respect correct execution order, dependencies between tasks must be specified explicitly.

Contrary to ALF, Zhao and Kennedy [25] have developed a dependence-based compiler for Fortran targeting the CBE. They use Allen and Kennedy's [26] *dependence matrices* to study dependencies in loop nests to optimally divide the code. They use a static model of task distribution based on a *fork-join* model of task spawning.

Beyond compiler technology, APIs were developed or ported to accelerate applications on the

CBE. In particular, an SPU implementation of the Basic Linear Algebra Subprograms API [27] is distributed by IBM to enhance the programming of scientific applications. FFTW [28] has also offered, in its latest version, support for computation on Cell [29] in its latest framework.

#### 1.5.1 Scheduling

Just as for any other parallel system, programming for the CBE involves a choice of runtime model. Statically allocated task distribution models are most common, and fit well with OpenMP and MPI. However, Blagojevic *et. al* show that dynamic adaptations can increase performance. Three Dynamic task distribution mechanisms were studied [30, 31].

The first mechanism presented by Blagojevic introduces task-level parallelism, by allowing fair sharing mechanisms of MPI SPU processes. The second attempts to evaluate the amount of loop partitioning necessary to optimize SPU use. Finally, the third studies the throughput of SPUs to throttle the granularity level of MPI tasks, thereby avoiding local maxima. In spite of the overhead one may expect from such an approach, it proves to be of little consequence, and good performance is achieved. Unfortunately, this appcoach is restricted to very large, completely regular applications, and does not apply to irregular tasks. It shows, however, the potential of dynamic adaptability in CBE task distribution.

## Chapter 2

# Parallel Programming and Functional Languages

Long before the age of multi-core processors, researchers attempted to accelerate large, complicated problems using several computers computing different aspects of the problem. The problems encountered then are fundamentally the same as those parallel programmers face now. There are several hazards implicit to computing in parallel. For instance, several actors may share physical resources such as memory, disks, etc. and require OS support. Yet the biggest difficulties lay in data coherence; if several threads must share a common data element, the order in which reads and writes occur could have a corrupting effect on the result computed. Synchronization is also an important problem: a thread should not use data created by another thread if that data's processing is not complete.

Many of the solutions to these problems tend to be solved through some amount of hardware support. Atomic primitives allow read and write operations given memory locations that do not overlap to cause unexpected behavior. However, many of the issues are also directly dependent on the problem posed, and require software solutions. Coherent access to data must respect dependencies in the data access patterns that the application requires. Surreptitious problems such as *deadlock* can occur as well, when several resources depend on one another to advance execution, causing none to do so.

#### 2.1 Parallel Programming Design

Given these challenges, integrated solutions to parallel programming have been developed [32]. The first such solution offered was High Performance Fortran [33] (1993). Ulterior solutions fundamentally differed on the memory model used; processing elements (PEs) may share a global memory space or not. In the first case, much care must be taken to guard against data hazards and to ensure proper synchronization. OpenMP [34] is the most widely used language extension in shared-memory parallel systems architecture. It provides a set of preprocessor directives to indicate to compilers the method by which they are to divide single-source code into threads and enforce synchronization.

In the alternate model, every PE operates independently. Parallelism and synchronization is achieved by means of the underlying communication architecture of the system. PEs thus communicate through *message passing*. In the popular Message Passing Interface (MPI) [35], library routines are provided to offer developers an abstraction of the low-level communication mechanism. A certain advantage of the distributed memory model is the modularity and scalability it provides to parallel system architects. Indeed, if library routines can adapt to different systems, there is little added complexity to adding hardware.

These two solutions are used as extensions to existing programming languages commonly used in High Performance Computing (HPC). However, these and others impose difficult decisions on developers. If an application is to be parallelized, it must be divided in moderately independent threads of computation. If an excessive amount of synchronization exists between threads, a large amount of time will be lost as threads wait for one another. Further, any communication incurs an associated overhead. The decisions taken in the division of code are thus quite consequential to performance.

As a natural evolution from machine-level code where instructions are performed in a sequen-

tial way, current programming languages dictate, step by step, the order in which individual quantas of computation must be executed. The extension of such languages becomes naturally awkward as the number of concurrent processes increase; it is quite difficult to transform a sequential approach into a parallel one. Some studies on the efficiency of novice parallel programmers expose that current solutions are quite cumbersome and difficult to use, and have a rather steep learning curve [36, 37].

#### 2.2 Task Partitioning

No matter what tool is used in parallelization, parallel code must be divided in separate units, as it must be run on separate processors. The paramount issue thus becomes the efficient and correct division of the code, and a proper analysis by a user or compiler is required

The parallelism present in an application can be exploited in several different ways. A code may have two independent and unrelated computations to perform, the results of which are required after a long period of time has elapsed. They can both be computed simultaneously and a blocking mechanism ensures both work units have completed to consume their results. A more common source of parallelism, however, is from loops. Indeed, typical programs use loops very frequently and at several levels of hierarchy. It occurs quite often that loop iterations are mutually independent, a property that offers a clear opportunity for parallel partitioning. Loop iterations with mutual dependencies also have the potential for parallel execution and deep mathematical analysis has developed several analyses of the problem, starting with Lamport [38].

The partitioning problem is a mathematical analysis of a set of data distributed along three axes, or *spaces* [39]:

- 1. the *iteration* space, or the uniprocessor equivalent of the time progression of a loop,

- 2. the *data space* representing the subset of array elements accessed

- 3. the processor space to which individual or groups of iterations are assigned.

The task partitioning problem can thus be restated as the search for hazard avoiding concurrent accesses to data across the iteration space.

A location on iteration space is generally denoted by the use of an *index* associated to the loop. In the simple example:

Example 1.

int X [20];

for(i=0; i<10; i++)

X[i+5] = X[i];</pre>

the loop index is denoted by the variable i. The data space of the variable X is the subset of values indexed from 0 to 15 as all these locations will be read or written to. It can easily be seen that the loop can be divided into two parts. In the first five iterations, the element of X written to is not one of the original values of the array. However, the next five iterations are those that were accessed in the first part. The direction of the iteration axis must thus be respected in the computation of the loop.

The observation that led to the division of the loop in two parts is derived from the analysis of the array indexes accessed. In our example, both indexes are linear equations in *i*, and are said to be *affine* in *i*. An affine expression is defined as follows:

**Definition 1.** An expression is affine with respect to a loop index variable if the expression applies a linear operation on the variable; the variable may be multiplied by and added to constants or variables themselves affine with respect to the loop index.

The presence of affine indexing indicates that the data access pattern is regular across all iterations. It does not, however, indicate that the iteration space can be directly mapped to a processor space of equal size, as we have already observed. Indeed, the loop bounds in Example 1 cause a data hazard across the fifth iteration. A data dependence analysis across loop bounds must then be applied.

It is evident that the loop bounds have a direct impact on the presence of data dependencies

across loop iterations. If the upper bound of *i* in our example was limited to 5, the loop would have been completely parallel. The impact of loop bounds is complicated further in the case of nested loops. These can be expressed by a set of linear inequalities, as shown in the following example devoid of data dependencies:

```

int X [20][100];

for(i=0; i<100; i++){

for(j=i; j<10; j++){

X[i][j] = 0

}

}

```

Four inequalities may be written in this case:

$$i \ge 0,$$

$$i < 100 \Leftrightarrow 100 - i > 0,$$

$$j \ge i \Leftrightarrow j - i \ge 0,$$

$$j < 10 \Leftrightarrow 10 - j > 0$$

and can be simplified in the general case using *Fourier-Motzkin analysis* [40]. In general, nested loops may be formalized as:

$$\mathbf{Bi} + \mathbf{b} \ge \mathbf{0} \tag{2.1}$$

In our example:

$$\begin{bmatrix} 1 & 0 \\ -1 & 0 \\ -1 & 1 \\ 0 & -1 \end{bmatrix} \begin{bmatrix} i \\ j \end{bmatrix} + \begin{bmatrix} 0 \\ 99 \\ 0 \\ 9 \end{bmatrix} \ge \mathbf{0}$$

Similarly, array references can be formalized as:

$$Fi + f$$

(2.2)

Let us determine what constitutes a data dependence. There are three possible cases:

- 1. **True Dependence**: a write operation is followed by a read. Inverting the order would cause the old rather than new value to be read.

- 2. Antidependence: a read is followed by a write, causing the opposite problem.

- 3. Output Dependence: two writes follow each other on the same memory location.

A data dependence is thus certain to be present if there is:

- 1. at least one write

- 2. both references are affine

- 3. the references respect the condition:

$$\mathbf{F}_1 \mathbf{i}_1 + \mathbf{f}_1 = \mathbf{F}_2 \mathbf{i}_2 + \mathbf{f}_2 \tag{2.3}$$

where  $i_1$  and  $i_2$  are members of  $Z^{d_1}$  and  $Z^{d_2}$  respectively.

Equation 2.3 represents a set of *Diophantine equations* that is solvable through the Greatest Common Divisor (GCD) theorem:

**Theorem 1.** A linear Diophantine equation:

$$a_1x_1 + a_2x_2 + \dots + a_nx_n = C$$

has an integer solution iff the greatest common divisor of  $(a_1, a_2, ..., a_n)$  divides C.

Theorem 1 is of great use in compiler theory; compilers may study array references in order to perform efficient partitioning using an array of techniques. Functional languages such as Haskell also perform the test efficiently at runtime using *memoization* [41].

#### 2.3 Functional languages

The difficulties of parallel programming were not lost on the HPC community in the past quarter-century. Extensive research has been done on the development of alternative programming languages. The most commonly used programming languages such as C/C++ and Java are termed *imperative languages*. These languages are typically a high-level abstraction of machine code. In the same way that microprocessors perform instructions one at a time, the high-level statements of imperative languages are expected to do so as well. The time progression of program execution is bound to the order in which statements are written.

As an alternative, functional languages were devised to work from a mathematical perspective. They originated with lambda calculus [42] and express computation as the relation between different functions. The mathematical rules of commutativity and associativity dictate the order (or disorder) in which different functions are evaluated. From this early model, several languages were developed.

The fundamental property of functional languages that allows compilers to evaluate code in different possible orders is **referential transparency**. This property states that the result of one expression does not change if it is executed at any time with the same set of inputs. An expression may thus be replaced by its equivalent value, or any other expression of equivalent value. As a consequence, functional code may not contain any form of state as is common in imperative languages. In an execution context, this allows a *runtime system* to decide on the appropriate timing for the evaluation of an expression at runtime. In parallel systems, different threads of execution may be computed in an order dependent on the availability of data and hardware resources.

The possibility of modifying the evaluation order of functional code has led to a schism in the functional programming paradigm. The computation of an expression can be delayed until the moment when the expression's value is required. The Haskell [43] programming language follows this *lazy* evaluation approach. It implements a "pull" model of evaluation that can lead the system to avoid wasteful computation. By contrast, *strict* evaluation performs

all the computations described by the code and thus *eagerly* advances program execution. Eager evaluation removes much overhead, since variables can be passed by value rather than through the use of symbolic data constructs. Strict programming languages are typically simpler to implement for this reason and several popular languages were developed under this model such as LISP (1958), ML (1973) and CAML (1985).

#### 2.4 Implementation of Functional Languages

The vast amount of flexibility offered by functional languages in a parallel context imposes several decisions on the following aspects of the compiler and runtime environment [44]:

- Evaluation Model: Code can be seen either as a set of functions to execute (graph reduction approach) or as the consumption of input data (dataflow approach).

- Storage Management: If the evaluation of expressions is distributed in time, so is the creation and consumption of data. Such dynamic management and intelligent garbage collection are paramount issues to a runtime environment.

- **Communication Model**: As threads are created dynamically, their placement may either cause the transfer of data or become a consequence of its physical location on a PE.

- Load Distribution: The assignment of a thread to a PE may be requested by it or forced unto it.

In the first evaluation model, functions are associated to data at runtime. A graph of operations thus needs to be reduced by applying these functions to others that may have yet to be evaluated. This suits particularly well lazy evaluation, as data need not be available for an expression to be activated. It is thus possible to recursively traverse a graph to extract from it data. The recursion mechanism used certainly requires the maintenance of a large stack. The structure of this stack and its dynamic behavior are the main concerns when tackling the issue of storage management.

Conversely, the second evaluation model advances program execution by maintaining a full view of the available data. New results are produced as valid inputs are directed to computation nodes. The path data elements follow is deduced from the input code through the study of data dependencies. The dataflow model therefore clearly follows an eager evaluation approach quite appropriate to strict languages such as SISAL [45]. Languages such as Id [46] and parallel Haskell (pH) [47] are however non-strict in spite of following this model.

In both these approaches, the thread life cycles can take three forms. In the first, a parent thread blocks until it receives a *notification* from all its child threads that their work is complete. The second, fork-join model, is a particular case of the first, where all child threads are identical to one another. In the third, the threads created become completely independent of their parent. The only guarantee of synchronization in this last model is the structure of the graph.

In multiprocessor systems, the storage management model is consequent to the high latencies in communication between processors. These long delays encourage developers to try to prefer to move data as little as possible. In non-strict languages, this involves a distributed stack with several branches (a "cactus" stack) that may be quite complex to maintain. The advent of multi-core processors with very-high speed buses puts back into question such approaches.

Finally, the load distribution model can be either passieve or active. An active model has a main processor designating subordinates to the computation of certain tasks. In the passive model, a processor waits to be idle to ask for work. This may cause some extra communication overhead, as a PE asking for work needs to send a message to perform its request, and the main processor to acknowledge it before sending the context. It may, however, help make the load distribution even if a fair task dispatch policy is implemented.

#### 2.5 Future of Parallel Programming

Consequently to the changes in hardware architecture, functional and parallel software paradigms must be re-examined. A new set of requirements must be written to lay a strong foundation for the future. Several new languages and APIs are currently emerging for several architectures and will be described and compared.

#### 2.5.1 The Berkeley Conclusions

A large team of researchers at Berkeley [5] studied the challenges facing mutli-core architecture designers and software developers. They drew conclusions for every aspect of the problem, from the silicon process to the new programming paradigms required. Concerning the new approach required to develop software for these new systems, the following conclusions apply:

- 1. programmers should easily develop highly parallel applications

- 2. all considerations must eye a future where 1000s of cores rest on a chip

- 3. future programming models must abstract away the underlying architecture

- 4. programming models must support a wide scope of parallelism

- 5. microprocessor architects must sacrifice performance improvements if the use of new features is not evident to programmers

- 6. operating systems must undergo a dramatic re-thinking, bringing about support to virtual machines

The Berkeley team arrives at these conclusions by observing the current trend in favor of multi-core systems. As parallel microprocessors move into the mainstream, software must make use of the new resources available as it is in fact the primary goal of any hardware advancement to increase the efficiency of the code written. Developers may not be capable of taking advantage of resources available to them, either because of the difficulties of parallel programming or of a lack of knowledge of the architecture. The difficulties of present-day parallel programming thus constitute a first hurdle to overcome. Also, it occurs quite often that an intimate knowledge of the underlying architecture be required to take fully advantage of the resources available. This problem is abundantly apparent when programming for the CBE, as communication between processors is explicit and requires great knowledge of its bus. Any new approach to parallel software development must thus provide tools capable of bridging the gap between programmers' capacities and the architectures capabilities.

Further, it is paramount to keep an eye on the future of hardware. It is entirely conceivable that microprocessors available in a few generations will have thousands of cores. Such massively parallel engines would be impossible to program efficiently using current tools. Further, for these enormous chips, it is quite likely that several different core types will be present at once, each demonstrating different performance capabilities (e.g. SIMD, superscalar, VLIW, etc.). The new tools available must then be able to extract parallelism from an application at several levels: first to distribute it to clusters of cores, then amongst them, and finally at the word, byte and bit levels.

Virtual machines will become an integral step of thread management within an application, as several threads will be allocated to a "black box" by means of processor virtualization [48]. Management of such systems can become quite complex as its size affects memory coherence, I/O use and process communications, possibly requiring a significant amount of changes to modern operating systems.

#### 2.6 Emerging Languages and Platforms

Parallel to the development of CPUs, the computational power of GPUs has dramatically increased. This development has spurred interest in using GPUs for general purpose computing, dubbed *GPGPU*. GPUs have always been used as real-time systems; a resident code

handles *streaming* input to render an image. Rather than an image, it may output useful computation results. These are returned to the host CPU and Main Memory, implementing a *host/device* programming model. The remaining challenge is to dynamically send code to the GPU. The Brook programming language developed at Stanford [49], as well as NVIDA's CUDA [50], implement extensions to C as a solution. Brook is now part of AMD/ATI's solution to its future stream processors. OpenCl, a forthcoming open standard API for parallel programming with strong industrial backing, follows the same approach albeit without a new grammar.

Brook approaches the streaming model by creating a *stream* type to variables. Device *ker-nel* functions expect such inputs and conceptually operates upon them as they continuously arrive, in a fully parallel fashion. The inputs are typically memory arrays on which a **streamRead(source, destination)** function is applied, then fed to a kernel. For its part, CUDA requires of the programmer much knowledge of the underlying hardware. It extends C/C++ with modifiers to functions and variables to access different aspects of its hardware units. For instance, the **\_\_host\_\_, \_\_global\_\_** and **\_\_device\_\_** function modifiers respectively indicate that a function is written for the host CPU, an entry point from the CPU to the device, and an internal device function. Similarly, modifiers can specify the location of variables on the different memory hardware elements of the GPU. As in Brook, *kernels* represent device code. However, an elaborate API exists to perform inter-kernel communication. Further, kernels are launched in blocks of threads that may share memory. A limited number of such threads in a block is allowed however, and language constructs provide means to subdivide excessively large groups of threads into a conceptual 2-D grid of thread blocks.

Not to be left behind, functional languages also offer great promise. Already, Microsoft found its experimental F# language, a variation of OCaml, itself a derivative of ML, to be so promising that it will incorporate it into its .Net framework. This development is sure to be a boon to functional programming as a whole, as one of the main issues that plagued the development of functional programs is the lack of library support [51]. Unfortunately, it is still unsure what multiprogramming advancements F# will bring.

Older languages may also be revived thanks to current hardware trends. Erlang [52] (1987), a robust open source functional language developed at Ericsson has supported parallel programming for a long time using message passing. The Fortress project [53] held promise as well, but its future is rather in doubt. However, Haskell, with its large user base, holds the most promise for parallel functional languages even though multi-core implementation of its parallel versions have not yet surfaced.

### 2.7 Squid/SRE: an integrated three-step solution

Our approach to our multi-core programming framework design starts from the ground up. Given the intricacies and tediousness of parallel programming, our prime objective is to minimize the programmer's involvement in low-level details and to leave most of the optimization effort to the compiler itself. It follows quite logically then that the program should follow conventional single-thread programming, leaving all the partitioning, synchronization and optimization decisions to the compiler.

Our solution is certainly an extension of the functional progamming models developed for multiprocessors. It is novel however in its targeting of multicore processors, and the CBE specifically. This solution thus stands clearly opposite gcc that performs no data partitioning and focuses on the explotiation of ILP. Our solution offers to abstract away **all** low-level considerations in roughly the same manner as ALF. However, NCC/Squid removes the programmer's responsibility of parallelizing code. This decision to take responsibility for virtually all difficulties of CBE programming may hinder its performance, but could prove to be a good basis upon which to perform research in parallel programming. Squid studies data dependencies in much the same way as Zhao (*c.f.* Section 1.5), its analysis is enhanced through the analysis of a functional language.

As a first step, we thus propose NCC, a new programming language constructed with the aim of voiding the difficulties of multi-core programming. NCC provides constructs that simplify the compiler's code analysis while remaining intuitive to the user. The strength of NCC is its ability to expose parallelism and synchronization requirements so a compiler, Squid, may break up and optimize the programmer's code. NCC and Squid, are described in Chapter 3. Prior exposure to Mitrion-C [54], a high-level hardware description language, provided an interesting starting point. Mitrion-C is a strict functional dataflow language that is used to generate application-specific processors on field-programmable gate arrays. We made several important modifications to the language design. Some of its particularities were kept, but its many constructs were discarded, as they either did not apply to software, or were simply tedious to use. However, NCC follows the strict dataflow functional language basis of Mitrion-C.

In a second step, we elaborate on our design of the Squid compiler. Squid intends to perform a high-level analysis of input NCC code and adapt it to multi-core architectures in general and to the Cell Broadband Engine in particular. As it stands, Squid targets the CBE specifically, although the approach it takes in studying NCC code and treating it is applicable to most multi-core architectures.

Squid parses the input code using NCC's language definition. It then analyzes the code in order to divide the input code into *tasks* and *supertasks*. Tasks are a collection of C functions that target the SPU architecture. Supertasks are C++ classes that interact with the runtime environment and direct code execution. The generation of C/C++ code allows programmers to use legacy code and libraries developed for the CBE architecture.

Given the several levels of hierarchy involved in any code, supertasks may manage Tasks, child Supertasks, and a mix of the two. The relationship between the different levels of hierarchy and within the hierarchy is very much a function of the data dependencies exposed in code analysis, and the study of these dependencies will be the basis of the runtime environment. Indeed, in order to optimize the time the SPUs stay busy, we have opted for a dynamic management of tasks and supertasks, the details of which will be elaborated on in the next chapter. This approach has several effects in compilation and particularly in task partitioning. As a final step, we describe the Squid Runtime Environment (SRE). The SRE is responsible for runtime management of tasks and supertasks, and the interaction with the underlying hardware. The SRE follows a host/device approach. In its application to the CBE, the PPU runs two POSIX threads: the first is the host, and manages I/O and all functions that do not pertain to the accelerated code, while the second runs the SRE. The SRE is described at length in Chapter 4. The SRE acts as a portal to the accelerating SPUs. In this model, the host thread calls functions to be accelerated by the "device", by linking them to the SRE. These functions, of course, were written in NCC and are the product of Squid's compilation.

#### 2.7.1 Why NCC/Squid/SRE

The Berkeley conclusions described in Section 2.5.1 provide a strong basis for decisions in our approach to the design of NCC:

- NCC is easy to use;

- The partitioning method used by Squid can easily extend to an increase in the number of cores;

- NCC has no construct linking it to the CBE or any other architecture;

- NCC's nested parallelism can allow it to exploit several levels of granularity;

- The two-layered approach of both language and runtime environment can adapt generated code to complex architectures;

- The SRE currently exploits existing OS resources;

These justification validate in our view the approach taken to multicore development. A complete description of the NCC language, Squid's techniques and algorithms, and the SRE's mechanisms are described in the chapters that follow.

# Chapter 3

# NCC/Squid

In this chapter, we shall describe the first two steps of our solution. First, high-level design decisions in the design of NCC are justified, then the syntax, operators and constructs are explained. The task partitioning mechanisms proper to Squid are then described in some detail, in order to elucidate the relationship between the division of code at compile time and its distribution at runtime.

# 3.1 Design of a Dataflow Language

There are typically two levels of granularity in multi-core architectures from which to exploit parallelism. The first, very coarse, distributes code and data among several processing cores. The second is usually very fine, and typically consists of taking advantage of data locality. Every program must then make intelligent use of these two granularity levels and divide the code appropriately. This work attempts to remove nearly all code partition decisions from the user. Therefore, it is very important for the compiler to benefit from the maximum amount of freedom in analyzing and partitioning the code.

If the code can be divided at virtually any point and at any depth, one must ensure that these actions do not compromise application integrity. The language must therefore respect referential transparency described in Section 2.3. Referential transparency guarantees application integrity, but is not sufficient to construct a graph that is easy to partition. Therefore, we add the requirement that the dataflow be explicit. An explicit dataflow graph built in this way represents a tree of nodes representing data.

Familiarizing with a new computer language is always a challenge, especially when the migration to functional programming imposes a paradigm shift on the developer. Learning NCC is expected to be difficult as well as it forces several constraints that are often unusual, and permits habits that are typically forbidden in most languages. For these reasons, NCC constructs will remain as close as possible to common ones such as C, MATLAB, and python.

NCC code will follow largely the same structure as most imperative languages. Functions are the highest-level constructs that may contain several statements. Functions have inputs and outputs, all of which are typed. The body of a function contains a range of statements. Every statement assigns a value to one or more variables. These values may be the result of arithmetic operations, conditional statement constructs, or iteration constructs. NCC specifies the peculiar requirement of enforcing a single-assignment rule to variables. The modalities and justifications for this important rule will be elaborated on in Section 3.2.3.

#### 3.1.1 Variables, Data Types and Syntax

The lowest-level construct in NCC as in most imperative languages is the variable. In the frame of referentially transparent language, variables represent no more than data. The data can take the form of an n-dimensional array or may simply remain scalar. Each and every variable is associated to a type, in just the same way as it is in C. However, the variable's type declaration is not always necessary. The temporal and structural modalities of variable declarations and assignments are thoroughly discussed in Section 3.1.2.

NCC defines the same data types as ANSI C: char, short, int, long, float, double as these types are inherent to all modern processors. As it was previously noted, the dependency to every variable is explicit. It follows henceforth that so is its type, given a set of initial conditions. This observation voids the need to declare a variable's type in straightforward cases. Some functional languages infer types even for ambiguous cases; however, we choose to force type explicitness in all ambiguous cases.

#### 3.1.2 Scopes

The most important level of granularity in NCC is the scope. A scope is defined as such:

**Definition 1.** A scope is a group of statements containing a limited number of variables, expliciting some as outputs. They can be seen as *black boxes* the output of which could be replaced by the equivalent value by virtue of referential transparency. A scope may contain other scopes as part of statements.

The scope can thus be seen as a proverbial black box with inputs and outputs, thereby enforcing referential transparency at this level. However, this definition and the associated rules are not sufficient to build a dataflow graph. Additional rules are thus necessary to be applied to statements within a scope to build such a graph *within* a given scope. It is already established that scopes can inherit variables (data) as inputs, and these will constitute entry points to the graph. Referential transparency specifies that 'states' may not exist, i.e. that a block of code may be called at different moments with different outputs must give the same outputs. Similarly, outputs must be clearly defined in every construct to provide exit points to the graph.

Since NCC must describe dataflow rather than temporal flow, there must be no ambiguity in the actual flow of the diagram. We must then consider potential sources of ambiguity. Every variable's assignment can be considered as a node in the dataflow graph. Variables are described using identifiers. These identifiers represent the variable's node throughout the scope. Therefore, performing an assignment to a given variable more than once creates several nodes identified by the same identifier. This behavior is clearly ambiguous and must be forbidden. A more subtle ambiguity may occur in a case of circular referencing. Indeed, if two variables refer to one another in the same scope, how can the value of either be evaluated? One solution is typically to set initial values to one of the two. Assigning initial values within the scope clearly constitutes multiple assignment. Circular referencing is not strongly forbidden in NCC, and is in fact one of its most significant features. However, the danger of ambiguity forces us to strongly curtail its use.

These observations lead us to enforce the dataflow model through the following rules:

- 1. Any variable may be assigned to once and only once in a given scope.

- 2. Every construct must clearly indicate its outputs.

- 3. Circular referencing is not allowed with the exception of loops, in which case an initialization value must be set outside the scope.

These rules cause an important potential **relaxation** in programming use: *code flow does not need to dictate temporal execution flow.* In other words, the programmer does not need to write code in the order it is expected to be executed. Since every variable is assigned to once and represents solely data, we can represent every scope as a directed acyclic graph (DAG)

**Definition 1.** A directed acyclic graph, also called a DAG, is a directed graph with no directed cycles; that is, for any vertex v, there is no nonempty directed path that starts and ends on v.

Every node in the DAG represents a variable which in turn represents data, toward which a *single* edge only is directed. The temporal flow is thus implicit in the DAG, no matter the order in which it is built.

The example depicted in Figure 3.1 demonstrates how two statements written in different order render the same graph.

Fig. 3.1: Inverting the order of statements does not change the DAG.

Let us introduce the more complex example of matrix-vector multiplication of Figure 3.2. The code contains 3 scopes, denoted in the figure by 'scope 0-2'. Notice that the initialization to the variable to\_sum is written *after* the statement in which it is referred. Notice also that scopes 1 and 2 are nested, creating a natural *hierarchy of scopes*. This hierarchy is important in future considerations.

```

int [100] mmul(int[100][200] matrix, int [200] vector){

final = for(row in matrix){

result = for(ea, eb in row, vector){

to_sum = to_sum + ea*eb;

}(to_sum);

int to_sum = 0;

}(><result);

}(final);</pre>

```

Fig. 3.2: Matrix-vector multiplication expressed in NCC.

# 3.2 NCC constructs

NCC intends to cover the full spectrum of functional capabilities any complete language would. For this reason, it incorporates much of the same constructs found in the usual languages, such as arrays, loops, function calls, and conditionals. In spite of being an important

Fig. 3.3: Equivalent DAG of the code in Figure 3.2

feature in most languages, the C equivalent of the 'struct' does not exist for now in NCC, and is left as future work. Structures were left out of NCC not due to difficulties in their grammar or in the analysis of their use, but rather due to data alignment issues particular to the Cell Architecture.

#### 3.2.1 Scalars and Arrays

NCC ascribes to every data element not only a type but a dimension, each axis of which is described by a range, much in the same way as Java. It was already noted however that NCC does not permit pointer arithmetic and, by extension, pointer referencing. Arrays are thus handled by the programmer as data elements in the exact same way. Several operators are necessary to work with arrays to perform such operations as concatenation, subspanning, and multi-dimensional construction.

#### Concatenation

In the first case, it is quite common for scalars, arrays, or a mix thereof to be merged into a single array of elements to be processed further. Thereby arises the need for a concatenation operator, in this case Mitrion-C's '><':

a = c > < b;

where **b** and **c** are arrays of the same dimension. If **b** and **c** are multidimensional, every dimension's range must be the same so as to create an n-dimensional cubic matrix.

Arrays may also be merged by keeping their 'identity'. To that end, they can be included in a new array of arrays, that is, a multi-dimensional array, where each dimension represents a collection of arrays, each of which capable of being a collection itself. To build multidimensional arrays, NCC uses a bracket notation:

variable2D = [ v1D1, v1D2 ];

#### Range and Subspanning

Finally, it is of little use to build up vectors if parts of them may not be accessed. Similarly to MATLAB, NCC allows access to array parts through individual access and subspanning. To access an individual element of a variable's array, the bracket notation is used after the variable's identifier:

a = multidim[2][4][i];

As in all languages, the first bracket group represents the most significant dimension.

NCC further describes a simple way to automatically generate an array spanning a range:

[X1 .. X2]

where X1 may or may not be larger than X2, but must both be constants. This span can be used as data elements as well as array indexing. Its use as data elements is particularly important using loops (c.f. Section 3.2.3).

#### 3.2.2 Basic Expressions

In the simplest case, variables are assigned the result of arithmetic operations. The arithmetic operations and operators defined in NCC are exactly the same as those of ANSI-C, so as not to confuse a new programmer. Arithmetic operations are very simple to analyze from a dataflow perspective, as all variables referenced are inputs to the variable (node) being assigned.

#### 3.2.3 Loops

NCC defines two kinds of loops: the 'for' loop, and the 'while' loop. They differ slightly from other languages in their form, but also in their use. Typically, loops can be used in two ways:

- The number of loop iterations is known at compile time

- The loop count cannot be determined at compile-time

In the first case, several techniques have been developed to optimize performance, such as loop unrolling, efficient vector processing, etc. Further, it is quite often the case that the values of each iteration is saved, building up a vector of loop-assigned data. In that case, the loop size corresponds exactly to that of the vector. Therefore, contrary to languages such as C, the 'for' loop iteration size must be known at compile time to empower the compiler to easily apply optimization techniques.

In the second case, most if not all of these optimization techniques are no longer applicable. Further, an array cannot be efficiently re-sized across loop iterations for it to accumulate values. Therefore, NCC requires of the programmer to convert to 'while' loops in the common way these 'for' loops written in languages such as C/C++.

For example, the C/C++/Java loop:

```

for(i=0; i < b; i++){

...

out = ...

}

can be converted to:

int i = 0;

out = while(i<b){

...

i = i + 1;

...</pre>

```

```

}(a);

```

a = ...;