# Optimization of Fixed-Point Circuits Represented by Taylor Series and Real-Valued Polynomials Including Analysis of Precision and Range

## Yu Pang

Department of Electrical and Computer Engineering

McGill University

A thesis submitted to McGill University in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical Engineering

© Yu Pang, 2010

March, 2010

# **Acknowledgements**

I would especially like to thank my supervisors, Dr. Radecka and Dr. Zilic who give me an opportunity to do this research in which I am really interested, and make this thesis possible in the Department of Computing and Electrical Engineering at McGill University. I sincerely cannot help expressing how I should credit this thesis to their support and guidance.

Very special thanks are also due to my dad and mum and my wife, Mrs Aolei Cui, and all of my friends in IML lab for their great support and encouragement in whole remarkable days.

Many thanks to everybody who ever gave me help and support.

To Dad and Mum &

Aolei Cui

# **Table of Contents**

| LIST OF TABLES                                    | VI  |

|---------------------------------------------------|-----|

| LIST OF FIGURES                                   | VII |

| ABSTRACT                                          | XI  |

| CHAPTER 1 INTRODUCTION                            | 1   |

| 1.1 Design Flow                                   | 2   |

| 1.2 Verification Approach                         | 3   |

| 1.2.1 Simulation                                  | 5   |

| 1.2.2 Emulation                                   | 6   |

| 1.2.3 Formal Verification                         | 6   |

| 1.3 Introduction of Fixed-Point Arithmetic        | 11  |

| 1.3.1 Fixed-Point Range – Integer Portion         | 11  |

| 1.3.2 Fixed-Point Resolution – Fractional Portion | 13  |

| 1.3.3 Range & Resolution                          | 14  |

| 1.4 Thesis Goal and Contributions                 | 16  |

| 1.4.1 Compositions of AT and Extensions           | 16  |

| 1.4.2 Imprecise Circuits                          | 18  |

| 1.4.3 Range Analysis                              | 21  |

| 1.4.4 Exploration of Fixed-Point Circuits         | 22  |

| 1.4.5 Contributions                               | 22  |

| CHAPTER 2 BACKGROUND                              | 23  |

| 2.1 Function Representations                      |     |

| 2.1.1 Truth Table                                 |     |

| 2.1.2 Shannon Expansion                           |     |

| 2.1.3 Polynomial Representation                   |     |

| 2.1.4 Boolean Satisfiability                      | 27  |

| 2.2 Decision Diagrams                             |     |

| 2.2.1 Binary Decision Diagrams                    | 28  |

| 2.2.2 Reduced Ordered Binary Decision Diagrams | 28 |

|------------------------------------------------|----|

| 2.2.3 Multi-Terminal BDDs                      | 32 |

| 2.2.4 Binary Moment Diagrams                   | 32 |

| 2.2.5 Taylor Expansion Diagrams                | 34 |

| 2.2.6 Disadvantages of Decision Diagrams       | 36 |

| 2.3 Dynamic Analysis                           | 37 |

| 2.4 Static Analysis                            | 41 |

| 2.4.1 Interval Arithmetic                      | 41 |

| 2.4.2 Affine Arithmetic                        | 43 |

| 2.5 Alternate Methods                          | 48 |

| 2.6 Conclusion                                 | 50 |

|                                                |    |

| CHAPTER 3 COMPOSITIONS OF AT AND EXTENSIONS    | 51 |

| 3.1 Introduction of Spectral Transforms        | 52 |

| 3.1.1 Spectral Domain                          | 52 |

| 3.1.2 Various Transforms                       | 53 |

| 3.2 Arithmetic Transform                       | 57 |

| 3.2.1 Basic Definition                         | 57 |

| 3.2.2 Utilization of Spectral Techniques       | 60 |

| 3.2.3 Calculation of AT Coefficients           | 62 |

| 3.3 Extensions of the Arithmetic Transform     | 64 |

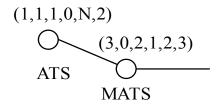

| 3.3.1 Mixed Arithmetic Transform               | 65 |

| 3.3.2 Sequential AT Extensions                 | 66 |

| 3.4 Composition Subroutines                    | 69 |

| 3.4.1 Composition of AT and MAT                | 69 |

| 3.4.2 Composition of ATS and MATS              | 71 |

| 3.5 Overall Composition Algorithm              | 73 |

| 3.6 Experimental Results                       | 76 |

| 3.6.1 ALU Circuit Implementation               | 76 |

| 3.6.2 CSA Circuit Implementation               | 77 |

| 3.6.3 MAC Transform                            | 79 |

| 3 6 4 Implementation of Hilbert Transform      | 80 |

| CHAPTER 4 BASIC ALGORITHMS                                 | 0.5 |

|------------------------------------------------------------|-----|

| 4.1 Taylor Series                                          |     |

| 4.2 Algorithm of AT Conversion by Taylor Series            |     |

| 4.2.1 Expansion Formula                                    |     |

| 4.2.2 Isomorphic AT Terms Combination                      |     |

| 4.2.3 Weights of Expanded Terms                            |     |

| 4.2.4 Other Discussions                                    | 90  |

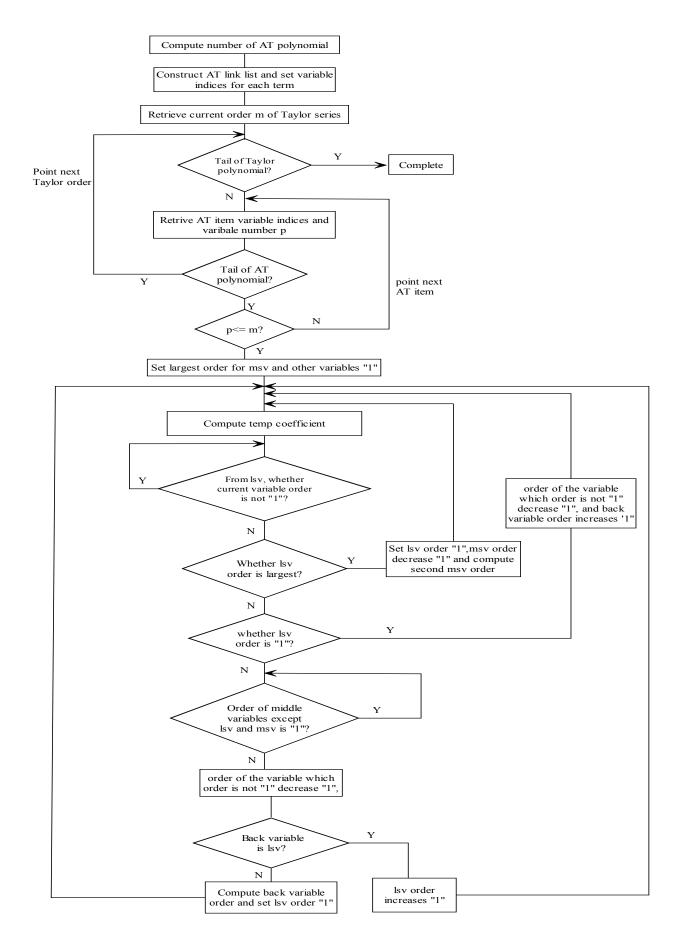

| 4.2.5 Flow of Conversion Algorithm                         | 93  |

| 4.3 Processing Multivariate Polynomials                    | 93  |

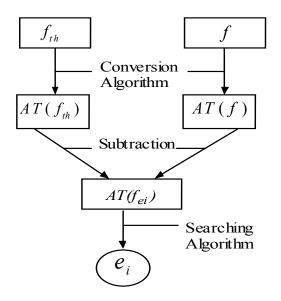

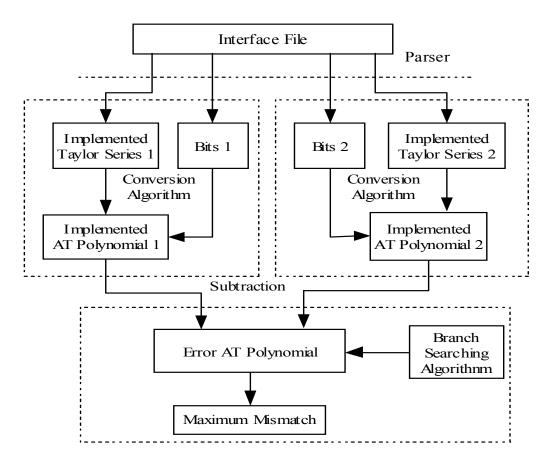

| 4.4 Imprecision Searching Algorithm                        | 97  |

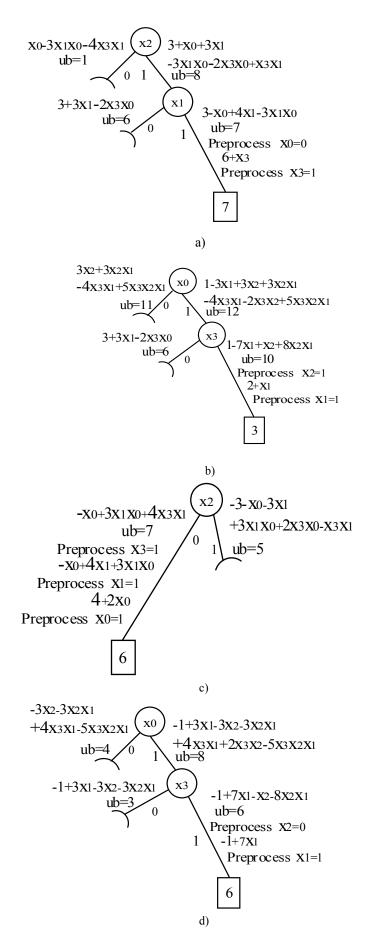

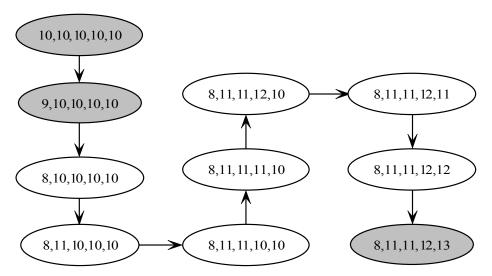

| 4.4.1 Basic Definitions of Branch Algorithm                | 97  |

| 4.4.2 Branch-and-Bound Searching Algorithm                 | 98  |

| 4.5 Experimental Results                                   | 101 |

| 4.6 Conclusion                                             | 102 |

|                                                            |     |

| CHAPTER 5 ANALYSIS OF PRECISION PARAMETERS                 | 103 |

| 5.1 Imprecise Arithmetic Computations                      |     |

| 5.1.1 Finite Wordlength                                    |     |

| 5.1.2 Arithmetic Transforms and Imprecise Datapaths        |     |

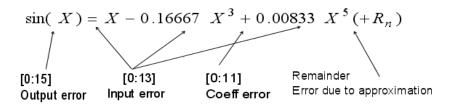

| 5.2 Function Approximation Error                           | 107 |

| 5.3 Input Bit-width and Quantization Error                 | 108 |

| 5.3.1 Effect of Finite Input Bit-width – Interval Analysis | 108 |

| 5.3.2 Tight-bound Interval Scheme                          | 110 |

| 5.4 Quantization of Coefficients and Output                | 111 |

| 5.5 Conclusion                                             | 112 |

|                                                            |     |

| CHAPTER 6 ALGORITHMS FOR PRECISION VERIFICA                |     |

| OPIMIZATION                                                |     |

| 6.1 Component Comparison                                   |     |

| 6.2 Verification of Implementations                        | 115 |

|    | 6.3 Finding a Feasible Implementation                              | 117 |

|----|--------------------------------------------------------------------|-----|

|    | 6.4 Designing Optimized Implementations with Constraints           | 118 |

|    | 6.4.1 AT Size as a Cost Function                                   | 119 |

|    | 6.4.2 Error Sensitivity                                            | 119 |

|    | 6.4.3 Constraint of the Smallest Area                              | 121 |

|    | 6.4.4 Constraint of the Minimum Delay                              | 127 |

|    | 6.4.5 Constraint of Interface Input Bit-width                      | 128 |

|    | 6.5 Experimental Results                                           | 130 |

|    | 6.5.1 Comparison of Two Implementations                            | 130 |

|    | 6.5.2 Verification of Imprecise Circuits                           | 133 |

|    | 6.5.3 Finding Implementations with the Smallest Area               | 134 |

|    | 6.5.4 Finding Optimized Implementations due to Various Constraints | 139 |

|    | 6.6 Conclusion                                                     | 141 |

| ~1 | A DEED E DANGE ANALYSIS                                            |     |

| CI | HAPTER 7 RANGE ANALYSIS                                            |     |

|    | 7.1 Disadvantages of Traditional Methods                           |     |

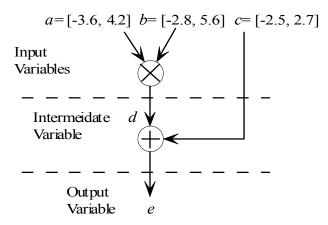

|    | 7.2 Datapath Analysis                                              |     |

|    | 7.2.1 AA Expressions.                                              |     |

|    | 7.2.2 Determining Quantization Bits for Uncertain Variables        |     |

|    | 7.2.3 Allocating Bit-widths for All Outputs                        |     |

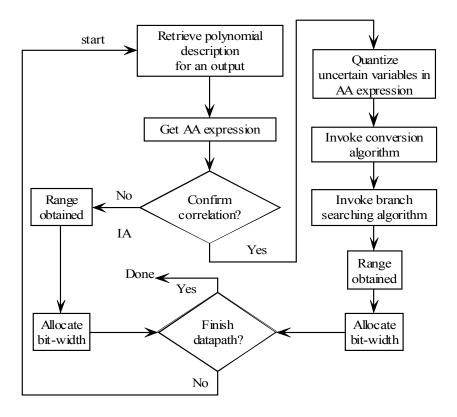

|    | 7.3 Algorithm for Calculating Ranges                               | 150 |

|    | 7.4 Experimental Results                                           | 153 |

|    | 7.4.1 Filter Polynomial                                            |     |

|    | 7.4.2 Dickson Polynomial                                           | 154 |

|    | 7.4.3 Multivariate Datapaths                                       | 154 |

|    | 7.4.4 Energy Spectral Density                                      | 155 |

|    | 7.4.5 Area of Optimized Implementations                            |     |

|    | 7.5 Conclusion                                                     | 157 |

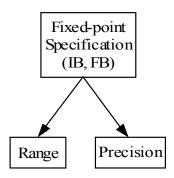

| Cl | HAPTER 8 COMBINING RANGE AND PRECISION                             | 158 |

|    | 8.1 Description of Fixed-Point Representation                      | 159 |

|    | 8.2 Analysis of Range and Precision                                | 160 |

| 8.3 Algorithm for Finding Optimized Implementations163 |  |

|--------------------------------------------------------|--|

| 8.4 Discussion of Cost Functions166                    |  |

| 8.5 Sequential Fixed-Point Circuits167                 |  |

| 8.6 Extension to Feedback Datapaths168                 |  |

| 8.6.1 Delay Units                                      |  |

| 8.6.2 FIR Filters                                      |  |

| 8.6.3 Linear Feedbacks - IIR Filters                   |  |

| 8.6.4 Non-linear Feedbacks                             |  |

| 8.6.5 Experimental Results                             |  |

| 8.7 Extension to Floating-Point Circuits180            |  |

| 8.8 Conclusion                                         |  |

| CHAPTER 9 CONCLUSION AND FUTURE WORK185                |  |

| 9.1 Conclusion185                                      |  |

| 9.2 Future Work                                        |  |

| <b>REFERENCES</b> 188                                  |  |

## **List of Tables**

| Table 3.1 | Norm functions for common word encodings                                       | 58        |

|-----------|--------------------------------------------------------------------------------|-----------|

| Table 3.2 | Definitions of the AT and its extensions                                       | 69        |

| Table 3.3 | Results for the ALU transform                                                  | 77        |

| Table 3.4 | Results of CSA transforms                                                      | 78        |

| Table 3.5 | Results of MAC transforms                                                      | 80        |

| Table 3.6 | Results of Hilbert transforms                                                  | 81        |

| Table 4.1 | Performance of Taylor series conversion                                        | 102       |

| Table 6.1 | Error and performance of various components on                                 | different |

|           | criteria                                                                       | 133       |

| Table 6.2 | Checking implementations whether to satisfy the error                          | bound in  |

|           | terms of given parameters                                                      | 134       |

| Table 6.3 | Optimized implementations with smallest area and perfor different error bounds |           |

| Table 6.4 | Result comparison with the paper [45]                                          | 136       |

| Table 6.5 | Error comparison of AA and our method                                          | 137       |

| Table 6.6 | Hardware area of optimized circuits                                            | 138       |

| Table 6.7 | Optimization of imprecise circuits due to constraints                          | 140       |

| Table 6.8 | Hardware delay and area for optimized implementations.                         | 141       |

| Table 7.1 | Comparison with AA for the filter polynomial                                   | 153       |

| Table 7.2 | Comparison of our method, AA and improved simul                                | ation for |

|           | Dickson polynomial                                                             | 154       |

| Table 7.3 | Comparison with AA for a multivariate datapath                                 | 155       |

| Table 7.4 | Our method vs. AA vs. SMT for energy spectral density                          | 155       |

| Table 7.5 | Area comparison of our method and AA                                           | 156       |

| Table 8.1 | Performance of the algorithm finding IIR ranges                                | 179       |

# **List of Figures**

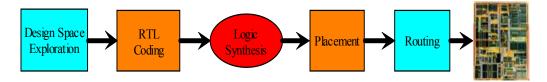

| Figure 1.1  | A typical ASIC design flow                                             | 2   |

|-------------|------------------------------------------------------------------------|-----|

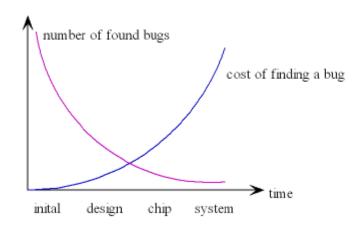

| Figure 1.2  | Comparison of detection time and cost of design errors                 | 3   |

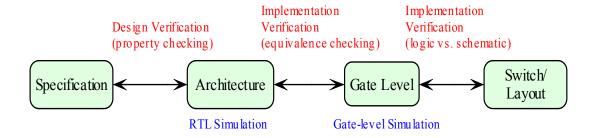

| Figure 1.3  | Design and implementation verification                                 | 3   |

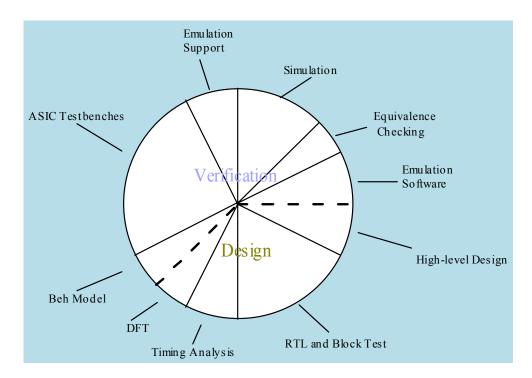

| Figure 1.4  | Breakdown of effort                                                    | 4   |

| Figure 1.5  | Different aspects of verification                                      | 4   |

| Figure 1.6  | Simulation in the development procedure                                | 5   |

| Figure 1.7  | The process model of formal verification                               | 7   |

| Figure 1.8  | RTL-to-gate equivalence checking                                       | 8   |

| Figure 1.9  | Idea of model checking                                                 | 9   |

| Figure 1.10 | Comparison of model checking and simulation                            | 10  |

| Figure 1.11 | Comparison of formal verification tools                                | 10  |

| Figure 1.12 | The basic idea of imprecise circuits                                   | 18  |

| Figure 1.13 | Comparison of two implementations                                      | 20  |

| Figure 1.14 | Optimized implementation with the smallest area                        | 21  |

|             |                                                                        |     |

| Figure 2.1  | Shannon expansion in variable x <sub>i</sub>                           | 26  |

| Figure 2.2  | Complete and ordered DD                                                | 29  |

| Figure 2.3  | Ordered DD                                                             | 29  |

| Figure 2.4  | Two OBDDs of Example 2.5                                               | 31  |

| Figure 2.5  | An example of ROBDD                                                    | 32  |

| Figure 2.6  | $MTBDD for f = 3x_1 + x_2 \dots$                                       | 32  |

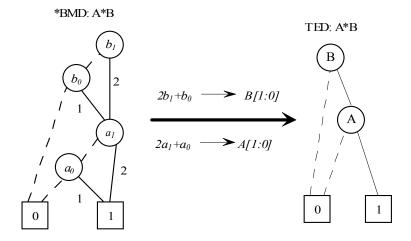

| Figure 2.7  | *BMD for unsigned fractional encoding                                  | 33  |

| Figure 2.8  | Abstraction of bit-level variables into algebraic symbols              | 34  |

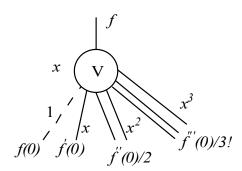

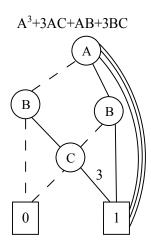

| Figure 2.9  | A decomposition node in a TED [12]                                     | 35  |

| Figure 2.10 | An example of an expression represented with TED                       | 36  |

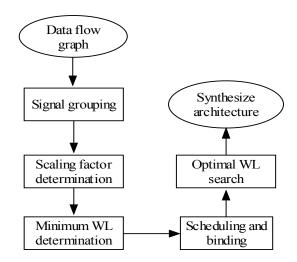

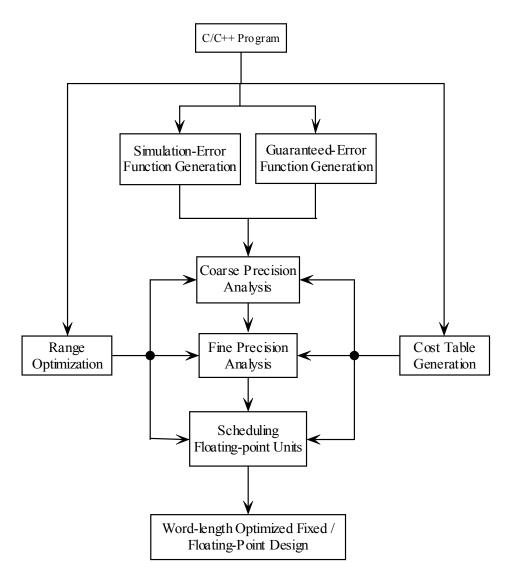

| Figure 2.1  | l Design flow of the architecture-level WL optimizati                  | ion |

|             | [19]                                                                   | 38  |

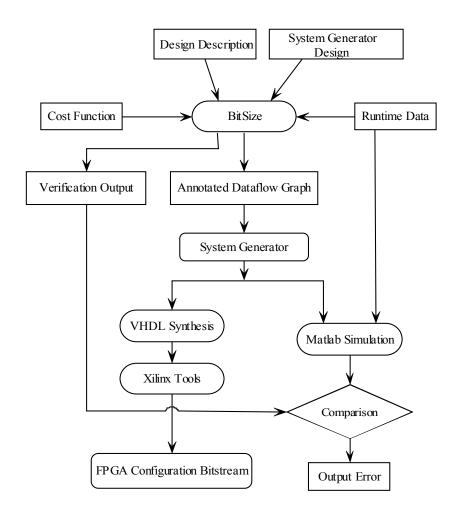

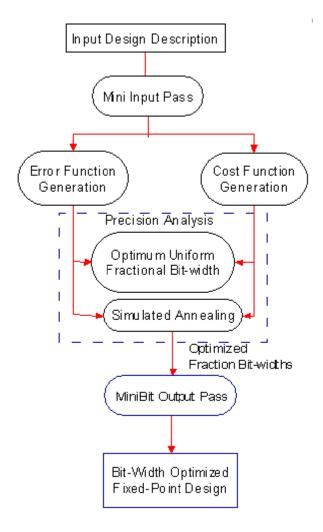

| Figure 2.12 | The tool flow of the method in [20]                                    | 38  |

| Figure 2.13 | The design flow of dynamic analysis in [21]                            | 39  |

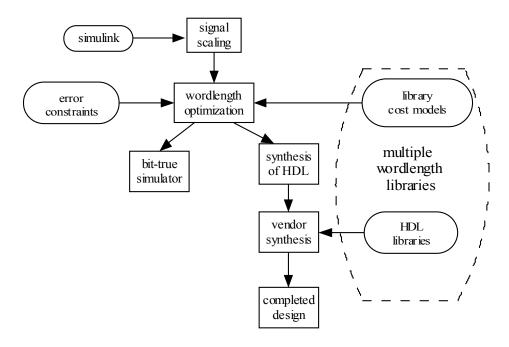

| Figure 2.14 | Overview of the synthesis framework in [23]                            | 40  |

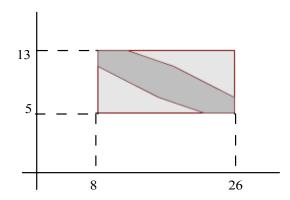

| Figure 2.15 | Joint range $(\hat{x}, \hat{y})$ of two partially dependent quantities |     |

|             | implied by their affine forms                                          | +4  |

| Figure 2.16            | An outline of the methodology in [41]                  | 46  |

|------------------------|--------------------------------------------------------|-----|

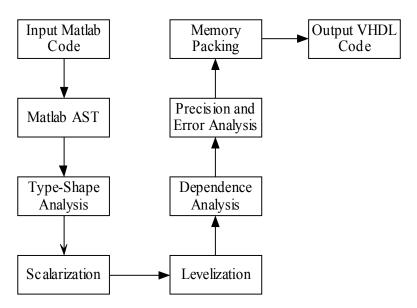

| Figure 2.17            | The tool of static analysis in [42]                    | 47  |

| Figure 2.18            | Synoptix design flow in [47]                           | 49  |

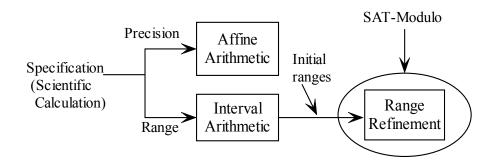

| Figure 2.19            | Flow of SMT technique in [55]                          | 49  |

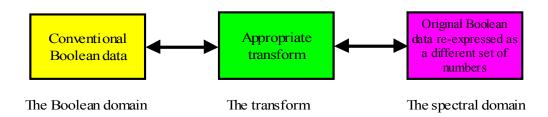

| Figure 3.1             | The spectral transform                                 | 52  |

| Figure 3.1  Figure 3.2 | Reed-Muller matrix for $n = 3$ and the polarity vector |     |

| rigure 3.2             | (010)                                                  |     |

| Figure 3.3             | A Kronecker transform matrix for $n = 3$               |     |

| Figure 3.4             | Sequentially ordered Haar functions for $n = 3$        |     |

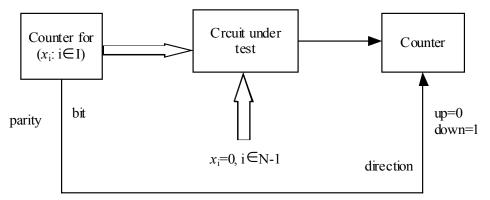

| Figure 3.5             | The spectral coefficient $a_i$ test structure in [65]  |     |

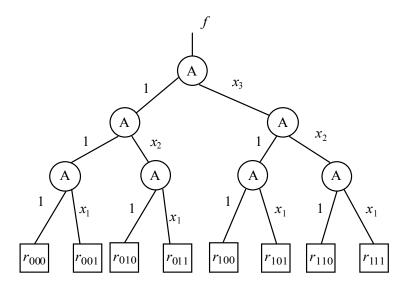

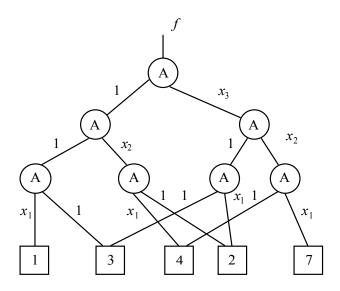

| Figure 3.6             | ACDD for n=3                                           |     |

| Figure 3.7             | ACDD of f in Example 3.6                               |     |

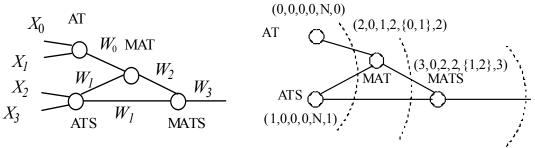

| Figure 3.8             | Binary encoding use for composition of ATs             |     |

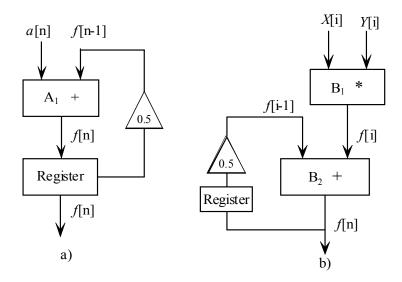

| Figure 3.9             | Add- and Multiply-Accumulate Loops                     |     |

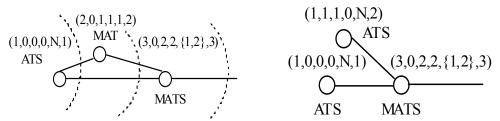

| Figure 3.10            | Algorithm of MAT and AT composition                    | 70  |

| Figure 3.11            | Algorithm of MATS and ATS composition                  | 72  |

| Figure 3.12            | The overall composition algorithm                      | 74  |

| Figure 3.13            | A circuit with 4 modules                               | 75  |

| Figure 3.14            | Node properties                                        | 75  |

| Figure 3.15            | Composing the MAT and the AT nodes                     | 75  |

| Figure 3.16            | Composing the MAT and the ATS nodes                    | 75  |

| Figure 3.17            | Composing the MATS and the ATS nodes                   | 76  |

| Figure 3.18            | An ALU model                                           | 77  |

| Figure 3.19            | 4-bit carry select adder                               | 78  |

| Figure 3.20            | Implementation of a MAC                                | 79  |

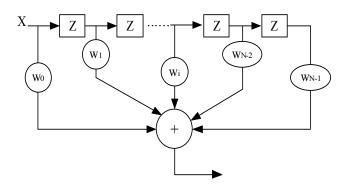

| Figure 3.21            | A FIR model to realize Hilbert Transform               | 81  |

| F: 4.1                 | Alancidan of annualing Toules in AT                    | 0.0 |

| Figure 4.1             | Algorithm of converting Taylor series to AT            |     |

|                        | Algorithm for converting a multivariate polynomial     |     |

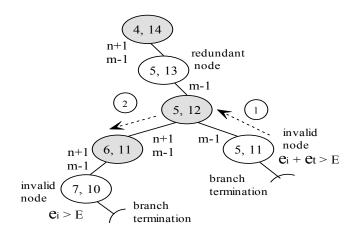

| Figure 4.3             | Searching the maximum absolute value in AT             | 98  |

| Figure 4.4             | Performing the imprecision algorithm in Example 4.5    | 100 |

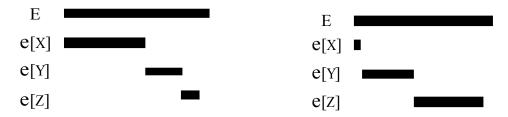

| Figure 5.1  | Imprecision due to the combined sources                                                       | 107  |

|-------------|-----------------------------------------------------------------------------------------------|------|

| Figure 5.2  | Value description of $X_{th}$ and $X_{th}$                                                    | 108  |

| Figure 5.3  | Computation of input quantization error                                                       | 110  |

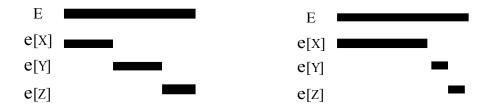

| Figure 6.1  | Comparison of two implementations                                                             | 114  |

| Figure 6.2  | Algorithm of computing imprecision between two implem                                         | nen- |

|             | tations of Taylor series                                                                      | .115 |

| Figure 6.3  | Algorithm of verifying the implementation                                                     | 116  |

| Figure 6.4  | A sequential method of fitting the error bound                                                | 118  |

| Figure 6.5  | The basic idea of sensitivity [21]                                                            | 120  |

| Figure 6.6  | Algorithm of finding the optimized implementation with                                        | the  |

|             | smallest area                                                                                 | 122  |

| Figure 6.7  | Search of optimized parameters in Example 6.1                                                 | 124  |

| Figure 6.8  | Algorithm for finding optimized parameters for real-value polynomials over multiple variables |      |

| Figure 6.9  |                                                                                               |      |

|             | node                                                                                          | 126  |

| Figure 6.10 | Two intermediate nodes from the initial node                                                  | 127  |

| Figure 6.11 | n-stage pipelined circuit                                                                     | 127  |

| Figure 6.12 | Algorithm of finding parameters for the minimum delay                                         | 128  |

| Figure 6.13 | Description of interface input bit-width                                                      | 129  |

| Figure 6.1  | 4 Algorithm of finding parameters for interface in bit-width                                  | _    |

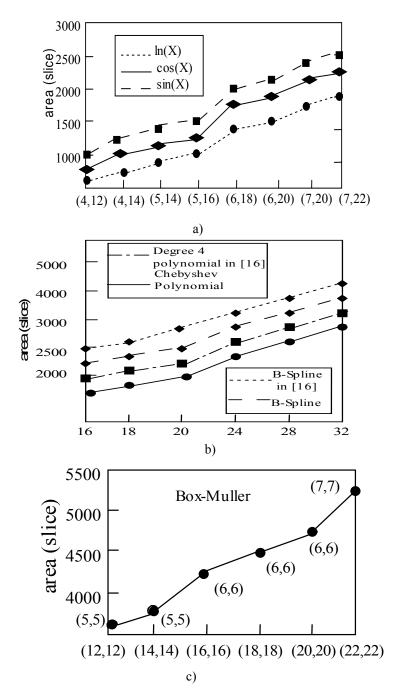

| Figure 6.15 |                                                                                               |      |

| - 18        | different Taylor terms and input bits                                                         |      |

| Figure 7.1  | Tradeoff between ranges and calculation times                                                 | 143  |

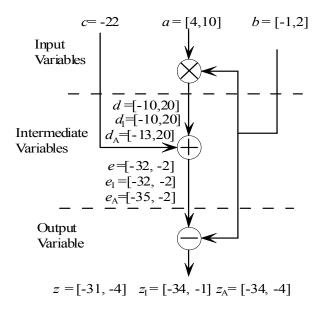

| Figure 7.2  | Example performing $z=ab+c-b$ by IA and AA                                                    | 144  |

| Figure 7.3  | Data format of the signed factional number                                                    | 148  |

|             | Algorithm of allocating bit-widths                                                            |      |

| Figure 7.5  | Algorithm for confirming correlation                                                          | 151  |

| Figure 7.6  | Algorithm of determining the quantization bit-widths uncertain variables                      |      |

| Figure 8.1  | Exploration of the fixed-point representation159                |

|-------------|-----------------------------------------------------------------|

| Figure 8.2  | The datapath of Example 8.1159                                  |

| Figure 8.3  | Fixed-point representation of variable a162                     |

| Figure 8.4  | Algorithm of finding the optimized fixed-point implementation   |

|             |                                                                 |

| Figure 8.5  | Finding next satisfying FBs165                                  |

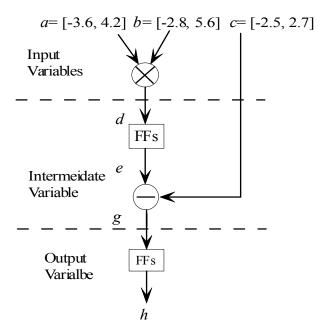

| Figure 8.6  | A sequential datapath with FFs167                               |

| Figure 8.7  | A delay unit with ranges                                        |

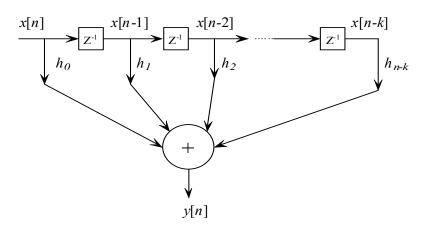

| Figure 8.8  | Implementation of the FIR filter with $k+1$ taps169             |

| Figure 8.9  | Ranges of a FIR filter                                          |

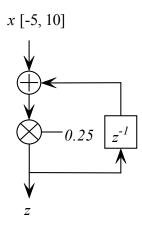

| Figure 8.10 | A circuit with a feedback171                                    |

| Figure 8.11 | A circuit like Example 8.5 with the different coefficient172    |

| Figure 8.12 | Algorithm of finding ranges of IIR filters173                   |

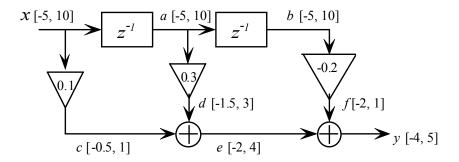

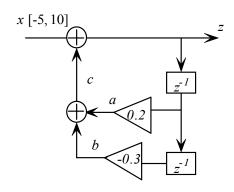

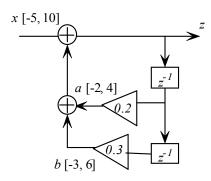

| Figure 8.13 | An IIR filter with two taps174                                  |

| Figure 8.14 | An IIR filter like Example 8.7 with different coefficients175   |

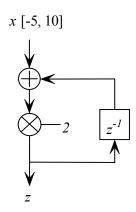

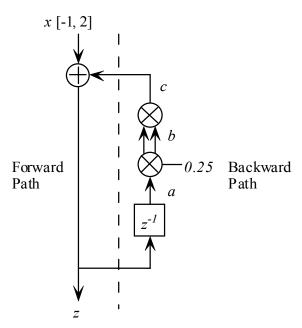

| Figure 8.15 | A circuit with a non-linear feedback176                         |

| Figure 8.10 | 6 Algorithm of finding ranges of circuits with non-linear       |

|             | feedbacks                                                       |

| Figure 8.17 | Range of floating-point numbers182                              |

| Figure 8.18 | Non-uniform distribution error in floating-point representation |

|             | 182                                                             |

# **Abstract**

In this thesis, our research focuses on fixed-point arithmetic circuits. Fixed-point representation is important in low power Application-Specific Integrated Circuits (ASICs) and in Programmable Logic Devices (PLDs). There are two aspects of the data representation problem: the precision problem and the range problem. Both of these are addressed in this thesis. We use the new technique based on Arithmetic Transform (AT) which is a canonical and efficient representation for digital circuits to avoid the disadvantages of past methods, and design an efficient algorithm which can compose detached modules to obtain the overall AT for a complex circuit.

First the precision problem is processed. The typical imprecise circuits expressed in terms of Taylor series are addressed in our research. Imprecise factors including finite terms and input quantization are analyzed by AT, and algorithms are designed to verify and optimize imprecise circuits in terms of different constraints. A hybrid method performs range analysis to handle the range problem and allocates the smallest integer bit-widths. Having devised the individual methods for precision and range analysis, we then combine the two together to find the optimized implementation. Furthermore, we extend the method to analyze floating-point circuits and feedback circuits.

The proposed algorithms in the thesis overcome disadvantages of past explorations. They are more flexible in processing both Taylor series and multivariate polynomials and obtain more precise results, resulting in better implementations under various constraints.

# Résumé

Dans ce manuscrit, notre recherche se concentre sur les circuits de l'arithmétique à virgule fixe. La représentation à virgule fixe est un facteur important dans les applications d'une faible consommation pour les ASICs (Application Specific Integrated Circuit) ainsi que les circuits logiques programmables (PLD). Au point de la représentation des données, généralement, il y a deux aspects de problèmes dont la précision et la gamme. Dans ce manuscrit, nous adressons principalement à ces deux éléments. Une nouvelle technique basée sur une transformée arithmétique (AT) est utilisée. Ceci est une représentation canonique et efficace pour les circuits numériques qui permet d'éviter les inconvénients des méthodes passées et de concevoir un nouvel algorithme efficace afin de composer des modules détachés en obtenant une AT le plus générale pour les circuits complexes.

Un travail préliminaire sur le problème de précision est effectué. Les circuits imprécis généraux s'expriment en termes d'une série de Taylor a été mis en œuvre dans notre recherche. Y compris des facteurs imprécis tels que les termes finis, la quantification d'entrée qui est analysée par AT ainsi que les algorithmes qui sont conçus pour vérifier et optimiser les circuits imprécis en termes de contraintes différentes. Une méthode d'une façon hybride est effectuée afin de traiter le problème de la gamme et d'allouer un entier le plus petit de bit-widths. Mise au point sur les différentes méthodes pour la précision et l'analyse de la gamme, nous combinons les deux ensembles afin de trouver une implémentation optimisée. En outre, nous étendons la méthode pour analyser des circuits en virgule flottante et les circuits de rétroaction.

Les algorithmes proposés dans ce manuscrit est de surmonter les inconvénients des explorations passées. Ces algorithmes sont plus flexibles dans le traitement de la série de Taylor et des polynômes à plusieurs variables. Ceux-ci nous permettent d'obtenir les résultats plus précis ainsi d'entraîner les meilleures implémentations sous diverses contraintes.

# **Chapter 1**

# Introduction

In this chapter, we first introduce the design flow for most common Integrated Circuits (ICs) and then describe verification approaches that include simulation, emulation and formal verification. Then, we state the research goals of thesis aiming at providing the solutions addressing the following three aspects of fixed-point circuit design: transform composition of a complex circuit, optimization of imprecise circuits, and range analysis.

## 1.1 Circuit Design Flows

With the development of modern material and production techniques, integrated circuits (ICs) reached a level of complexity beyond imagination of even a few years ago. In terms of Moore's law, the number of transistors doubled every 18 months. For example, Intel's Itanium II processor contains more than 10<sup>9</sup> transistors. Designing such complex circuits is a great challenge. The level of difficulties is lifted even higher by the restrictions on time-to-market. Hence, a systematic approach to design ICs is a must. Figure 1.1 outlines one of more commonly adopted approaches.

An idea for a new product originates usually from market analysis of customer needs. Then a team led by product managers describes in form of a specification the new design requirements. Once the specification is well formulated, the design process starts usually from behavioral modeling. As a result, initial algorithms are represented in hardware description languages (HDLs) like VHDL or Verilog, or even in higher abstraction languages, like SystemC. The correctness of the design refinement at this stage is checked by the comparison to the specification.

Figure 1.1: A typical ASIC design flow

After the behavioral model is verified, engineers generally partition the whole design into smaller and more refined blocks. Whenever possible, such blocks are often represented in terms of intellectual property (IP) cores, while HDL is used to design remaining elements at RTL coding. Once the design functionality and estimated performance satisfy the specification, the circuit is ready to be synthesized. This stage, performed automatically, often needs human intervention is terms of manual modifications necessarily such as design and insertion of boundary scan and built-in-self-test (BIST). After satisfying constraints such as timing, area and power, etc, a layout is conceived for fabrication.

# 1.2 Verification Approaches

Verification is a necessary procedure aiming to check whether the design is correct. It can be also viewed as a quality process that is used to evaluate whether or not a product, service, or system complies with a regulation, specification, or conditions imposed at the start of a development phase. In practice, verification is rarely fully completed while a given circuit is never stated fully correct since in common practice verification only shows the error presence rather than its absence.

Since errors found late in a design process can be potentially very costly, as shown in Figure 1.2, early detection is obviously critical. Hence, verification is performed at each stage of design development, from logic design, through scaling-up, to production, permeating almost all steps in ASIC design. Figure 1.3 illustrates a complete design flow for the development of an ASIC with verification.

Figure 1.2: Comparison of detection time and cost of design errors

Figure 1.3: Design and implementation verification

In general, it is estimated, that product-developing groups often spend

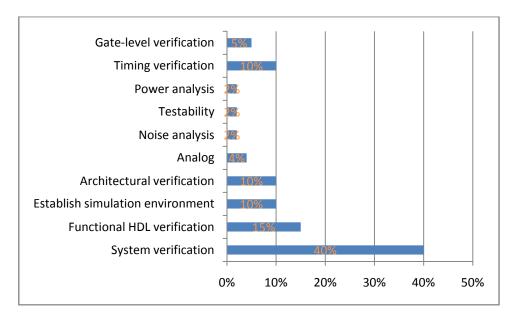

beyond 70% of the overall design time and cost on checking the correctness of their design [157]. The graph in Figure 1.4 describes a breakdown of the effort spent in each step and Figure 1.5 shows different aspects of verification.

Figure 1.4: Breakdown of effort

Figure 1.5: Different aspects of verification

From the above figure, it can be seen that time spent on verification at various stages of a design process is significant. Hence, engineers need a fast method to achieve the goal. The mainstream verification processes can be

divided into three categories: simulation, emulation and formal methods.

#### 1.2.1 Simulation-based Verification

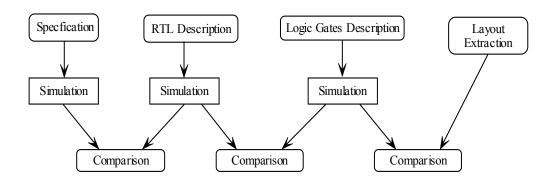

Simulation is a process in which a given design is exercised by a certain set of inputs [150]. Its idea is straightforward to comprehend, and the aim is to produce a set of test vectors (stimuli) used to check the design correctness. These test sets are called testbenches (set of input vectors, expected outputs, environment constraints, etc.). More precisely, based on the module response, which is compared to the specification, the correctness of the design is assessed. Simulation can be used throughout the whole development process. Figure 1.6 describes the idea.

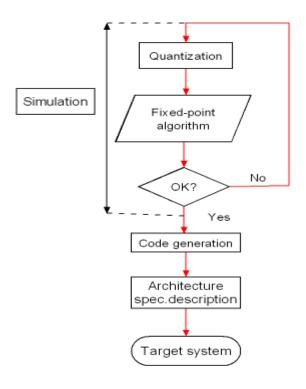

Figure 1.6: Simulation in the development procedure

Although the simulation method has obviously strong points, such as simplicity and easy testbench programming, there are some shortcomings we should note. First, sometimes it is not feasible to simulate all input sequences to completely verify a design. Suppose we want to test a 32-bit adder in this case - there are 2<sup>64</sup> combinations. If it requires 1 test/us, it will take 10<sup>12</sup> years to simulate that many vectors. Secondly, result comparison is often incomplete and it is difficult to compare results from different models and simulators. If the system grows larger, the number of possible states grows exponentially with increased number of possible event combinations. Furthermore, simulation can be effective to show the presence of bugs, but it is hopelessly inadequate for showing their absence.

#### 1.2.2 Emulation

Hardware emulation is a process that uses a piece of hardware, typically a special purpose emulation system, to imitate the behavior of a hardware system under design. As a special case, in-circuit emulation is very fast as it is performs a working target system in place of a yet-to-be-built chip, so the whole system can be debugged with live data.

High end hardware emulators provide a debugging environment with many features that can be found in logic simulators, and in some cases they even surpass their debugging capabilities [151]:

- The users can set a breakpoint and terminate the emulation process to inspect the design state, interact with the design, and resume emulation.

The emulator always stops on cycle boundaries.

- The users can watch all signal or memory contents in the design without probes before the run. While visibility is provided for past time events, an emulator can access the backward time steps which may be limited in some cases by the depth of the emulator's trace memory.

- The users can even back up time (if they save checkpoints) and re-run.

#### 1.2.3 Formal Verification

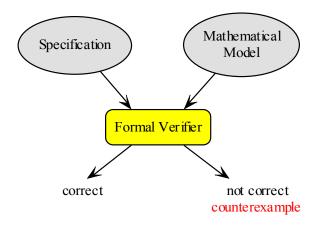

Formal verification is a process of proving or disproving the correctness of intended algorithms underlying a system with respect to a certain property using formal methods of mathematics. It can be used for verifying systems such as cryptographic protocols, combinational circuits, digital circuits with internal memory, and software expressed as source code [155].

A formal proof is necessary to verify systems based on an abstract mathematical model and the correspondence between the mathematical model and the nature of the system known by construction. Then formal verification is the process of constructing a proof that a target system will behave in accordance with its specification. Basis of formal methods, which distinguish them from simulations are:

Formal reasoning is used to prove that an implementation satisfies a specification,

- Correctness of a formally verified hardware design holds regardless of input values,

- Exhaustive exploration of all possible behaviors is conducted,

- A counter-example (proof) is presented if the property is incorrect while if correct, all behaviors are verified;

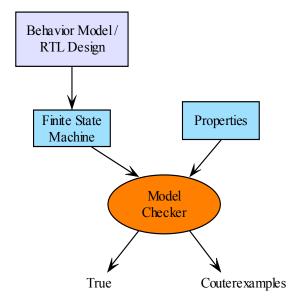

Figure 1.7 describes the formal verification model. A verifier is utilized to check whether the system model matches the system specification. If so, the verifier sends signal of correctness; if not, the verifier gives a counterexample.

Figure 1.7: The process model of formal verification

Further on, formal verification schemes have many advantages:

- Complete with respect to a property,

- Avoid generating expected output sequences,

- Helpful to detect and trace errors.

Since formal verification is based on model methods which are applied when a circuit description is given by propositional temporal logic, the three most widely model-based methods are *equivalence checking*, *model checking* and *theorem proving*. Equivalence checking formally proves that two representations of a circuit design exhibit exactly the same behavior. Generally, a wide range of possible definitions of functional equivalence covers comparisons between different levels of abstraction.

- Sequential equivalence checking considers machine equivalence, which

defines two synchronous design specifications functionally equivalent if

they generate exactly the same sequence of output signals for all valid

sequences of input signals clock by clock.

- A more general problem than equivalence checking is used to compare the

functions specified for the instruction set architecture (ISA) with a register transfer level (RTL) implementation, ensuring that the both models executing any program will cause an identical update of the memory contents.

A system design flow requires comparison between a transaction level model (TLM) and its corresponding RTL specification. The interest in this mode of checking increases in a system-on-a-chip (SoC) design environment.

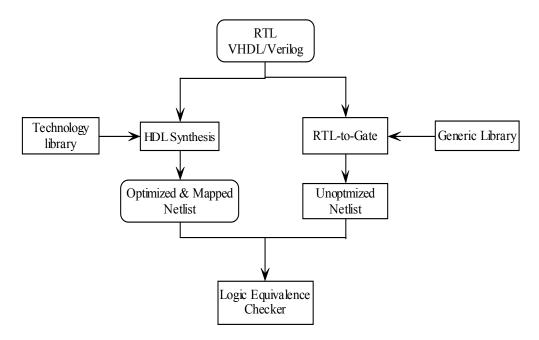

Figure 1.8: RTL-to-gate equivalence checking

Figure 1.8 illustrates the case of verification whether the RTL design and the modified netlist are equivalent. Because post-process often includes activities such as insertion of scan chain and some modifications, all these activities can not change the original function so equivalence checking can solve the problem.

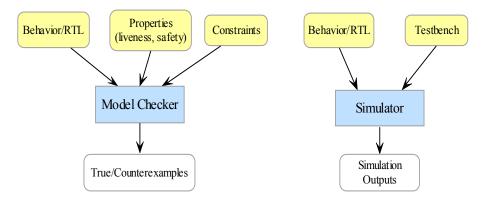

Given a model of a system, model checking is a process of automatic test whether this model meets a given specification. The system can be hardware or software, and the specification generally contains safety requirements such as critical states that may possibly crash the system.

The system model and the specification must be described in some precise mathematical language in order to solve such a problem algorithmically. The specification is formulated using a suitable language, and the verification process checks whether a given structure satisfies a given logical formula. The general concept can be applied to all kinds of logics and suitable structures. A simple model-checking problem is to verify whether a given structure satisfies a given formula in the propositional logic and it is useful to check circuit properties such as safety and liveness property. Model checking has characteristics:

- Searches the entire solution space, for possibly infinite duration

- Responds with YES or NO (if it terminates)

- Increasingly used in industry

- Can be automated for smaller blocks or when applied earlier in the flow

Figure 1.9 illustrates the basic idea of model checking.

Figure 1.9: Idea of model checking

From above figures, we see that although model checking and simulation can both verify RTL description, simulation relies on the testbenches, while model checking relies on mathematical reasoning represented by properties and constraints. Figure 1.10 describes their difference.

Figure 1.10: Comparison of model checking and simulation

Theorem proving decides whether a conjecture is a *logical consequence* of a set of statements (the *axioms* and *hypotheses*), which is used to prove that an implementation fits a specification by mathematical reasoning. The implementation and the specification are both expressed as formulas in a formal logic, and the necessary relationship - logical equivalence or logical implication - is described as a theorem to be proven within the context of a proof calculus. A proof system comprises a set of axioms and interface rules such as simplification, induction, rewriting. Authors in [159] describe how to express PSL's syntax and semantics in the PVS theorem prover and prove the correctness of a set of rewrite rules.

| Formal Verification Tools |                  |               |              |           |  |  |

|---------------------------|------------------|---------------|--------------|-----------|--|--|

| Supplier                  | Tool Name        | Class of Tool | HDL          | Design    |  |  |

|                           |                  |               |              | Level     |  |  |

| Commercial                | Commercial Tools |               |              |           |  |  |

| Synopsys                  | Formality        | Euqiv.        | VHDL/Verilog | RTL/Gate  |  |  |

|                           |                  | Checking      |              |           |  |  |

| Cadence                   | Affirma          | Euqiv.        | VHDL/Verilog | RTL/Gate  |  |  |

|                           |                  | Checking      |              |           |  |  |

| Cadence                   | FormalChec       | Model         | VHDL/Verilog | RTL       |  |  |

|                           | k                | Checking      |              |           |  |  |

| IBM                       | RuleBase         | Model         | VHDL         | RTL       |  |  |

|                           |                  | Checking      |              |           |  |  |

| Abstract                  | Lambda           | Theorem       | VHDL/Verilog | RTL/Gate  |  |  |

| Hardware                  |                  | Proving       |              |           |  |  |

| Public Dom                | ain Tools        |               |              |           |  |  |

| CMU                       | SMV              | Model.        | Own Language | RTL       |  |  |

|                           |                  | Checking      |              |           |  |  |

| Berkely                   | VIS              | Model/Equ.    | Verilog      | RTL       |  |  |

|                           |                  | Check         |              |           |  |  |

| Cambridge                 | HOL              | Theorem       | SML          | Universal |  |  |

|                           |                  | Proving       |              |           |  |  |

Figure 1.11: Comparison of formal verification tools

Figure 1.11 lists some typical tools. Although a variety of tools have been developed to perform formal verification, simulation is still a predominant method in verification because of the advantages of simple operation and relatively straightforward task of writing of testbenches.

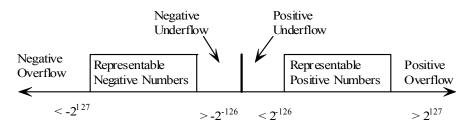

## 1.3 Introduction of Fixed-Point Arithmetic

Fixed-point arithmetic is of importance in low power designs, embedded systems and PLDs. Although floating-point data with single or double precision can construct algorithms more accurately, generally for signal processing algorithms such as FFT and DCT initiated from real values, significant processor overhead is required to perform floating-point calculations resulting from the lack of hardware based floating-point support. This disadvantage confines the effective iteration of an algorithm. In order to improve mathematical throughput or increase the execution rate, calculations can be performed by fixed-point representations which require a virtual decimal place in between two bit locations for a given length of data [133].

The labeling convention of the representation is as follows:

$$Q[IB].[FB] (1-1)$$

where IB = # of integer bits and FB = # of fractional bits.

Total number of bits used to represent the fixed-point number is yielded by the addition of integer bits IB and factional bits FB. The sum of IB+FB is known as the wordlength (WL) and this sum often corresponds to variable widths supported on a given processor. The fixed-point format includes two sections of integer and fractional content for the purpose of exploration.

## 1.3.1 Fixed-Point Range – Integer Portion

A fixed-point number is viewed as two distinct parts, the *integer content* and the *fractional content*. The integer range sets the number of *IB*, Eqn. (1-1), required to represent the integer portion of the number. *IB* itself can only hold

integer values because of the binary nature of a bit. Two different methods of calculating the number of integer bits match two types of numbers, unsigned and signed.

#### A) Unsigned Integers

The Equation (1-2) describes the unsigned integer by the minimum and maximum of any *IB* number.

$$0 \le r \le 2^{lB} - 1 \tag{1-2}$$

IB can be obtained by solving the required number as:

$$IB \ge [\log_2(r+1)]$$

where r is the floating-point variable being ranged. The square bracket is the ceiling function.

**Example 1.1:** Consider an unsigned variable r = 4.346:

$$IB = [\log_2(4.346+1)] = [2.43] = 3$$

Three bits are required for the integer portion of r.

#### B) Signed Integers

The previous equations cannot represent signed variables. The changed following equation denotes the definition for the integer contents of signed numbers  $(\pm r)$ :

$$-2^{IB-1} \le r \le 2^{IB-1} -1$$

Please note that the signed integer type is asymmetrical about zero. For instance, a signed 8-bit value ranges from -128 to 127. By solving for the negative constraint of the equation:

$$-2^{IB-1} \le r$$

we get:  $IB \ge [\log_2(-r)] + 1$

By solving for the positive constraint:  $r \le 2^{IB-1} - 1$

we get:  $IB \ge [\log_2(r+1)] + 1$

**Example 1.2:** If

$$r_{min} = -2$$

and  $r_{max} = 2$ ,

$$IB \mid_{r_{\min}} \ge [\log_2(-r_{\min})] + 1 = [\log_2 2] + 1 = 2$$

$$IB \mid_{r_{\text{max}}} \ge [\log_2(r_{\text{max}} + 1)] + 1 = [\log_2 3] + 1 = 3$$

IB must be 3 bits to satisfy the two constraints concurrently.

In the case of signed data type, the positive constraint is tighter than the negative constraint because of the asymmetry. It is common for users to define variable magnitude constraints that are symmetric about zero (for instance,  $-5 \le r \le 5$ ). The computation for *IB* can be generated uniformly by the equation:

$$IB = [\log_2(\max(abs[r_{\min} r_{\max}]) + 1)] + 1$$

**Example 1.3:** Compute a signed variable  $-4.43 \le r \le 4.43$ ,

$$IB = [\log_2(\max(abs[-4.43,4.43) + 1)] + 1 = [\log_2 5.43] + 1 = [2.45] + 1 = 4$$

#### 1.3.2 Fixed-Point Resolution – Fractional Portion

The number of FB sets the resolution for a fixed-point variable. The resolution  $\varepsilon$  of a fixed-point number is given by the following equation [134]:

$$\varepsilon = \frac{1}{2^{FB}}$$

Therefore the number of FB required by a particular resolution is defined as:

$$FB = [\log_2 \frac{1}{\varepsilon}]$$

**Example 1.4:** A signed variable r = -3.2782,  $\varepsilon \le 0.0001$ ,

$$FB = [\log_2 \frac{1}{0.0001}] = [\log_2 10000] = [13.288] = 14$$

The resolution is limited for a given wordlength and dynamic range of a variable. The WL of the variable must be increased to provide this resolution if a higher resolution is needed for a given range [134].

### 1.3.3 Range & Resolution

The integer and fractional parts of the number for a fixed WL consist of the full range and resolution. The combined range and resolution for an unsigned fixed-point number is defined by [133]:

$$0 \le r \le (2^{IB} - 1) \big|_{\varepsilon = 2^{-FB}}$$

The combined range and resolution for a signed fixed-point number is defined as [133]:

$$-2^{IB-1} \le r \le (2^{IB-1} - 2^{-FB})|_{\varepsilon = 2^{-FB}}$$

The integer and fractional bits are combined together and used to determine a standard WL that is large enough to hold all integer and fractional bits as:

$$WL_{required} \ge IB + FB$$

A representation U(IB, FB) where IB + FB = N for unsigned format is denoted to calculate the value of a fixed-point format. For an unsigned format, in the U(IB, FB) representation, the  $n^{th}$  bit, counting from right to left and beginning at 0, has a weight of  $2^n / 2^{FB} = 2^{n-FB}$ . Please notice that if n = FB the weight is 1. The value of a particular N-bit binary number x in a U(IB, FB) representation is given by the expression [134]:

$$x = (1/2^b) \sum_{n=0}^{N-1} 2^n x_n$$

where  $x_n$  is the bit n of x. The range representation is from 0 to  $(2^N-1)/2^{FB} = 2^{IB} - 2^{-FB}$ . For instance, the 8-bit unsigned fixed-point representation U(5,3) has the form

$$b_4b_3b_2b_1b_0$$

.  $b_{-1}b_{-2}b_{-3}$

where the bit  $b^k$  has a weight of  $2^k$ . Since FB is 3, the binary point is to the right of the third bit from the right (counting from zero), and hence the number has five integer bits and 3 fractional bits. This representation has a range of from 0 to  $2^5 - 2^{-3} = 32 - 0.125 = 31.875$ .

**Example 1.5:** U(6,2). This number has 6+2=8 bits and the range is from 0 to  $2^6 - 1/2^2 = 63.75$ . The value 4Bh (0100, 1011b) is:

$$(1/2^2)(2^0 + 2^1 + 2^3 + 2^6) = 18.75$$

Consider an N-bit binary word x as U(N,0). The one's complement of x is defined to be an operation that inverts every bit of the original value x. This

can be performed in the U(N,0) representation by subtracting x from  $2^N-1$ . That is, if we denote the one's complement of x as  $\tilde{x}$ , then:

$$\widetilde{x} = 2^{N} - 1 - x$$

The two's complement of x, denoted as  $\hat{x}$ , is determined by taking one's complement of x and then adding one:

$$\hat{x} = \tilde{x} + 1 = 2^{N} - x$$

**Example 1.6:** The one's complement of the U(8,0) number 05h (0000,0101) by hex representation is FAh (1111, 1010). The two's complement of the U(8,0) number 05h (0000,0101) is FBh (1111, 1011).

Considering signed two's complement fixed-point representation, we denote such a representation A(IB,FB) that IB = N-FB-1. The following expression gives the value of a specific N-bit binary number x in an A(IB, FB) representation:

$$x = (1/2^{FB})[-2^{N-1}x_{N-1} + \sum_{n=0}^{N-2} 2^n x_n]$$

Notice that the number of bits in the magnitude of the sum above has one less bit than the equivalent prior unsigned fixed-point representation. These bits are the *N-1* least significant bits because the most significant bit in a signed two's complement number is often referred to as the sign bit.

**Example 1.7:** A(11, 2). This number has 11+2+1=14 bits and the range is from  $-2^{11} = -2048$  to  $+2^{11}-1/4 = 2047.75$ .

Fundamental rules of fixed-point arithmetic are listed as follows [134].

- <u>Unsigned wordlength</u>: the number of bits required to represent U(IB, FB) is IB+FB.

- <u>Signed wordlength</u>: the number of bits required to represent A(IB, FB) is IB+FB+1.

- Unsigned range: The range of U(IB, FB) is  $0 \le x \le 2^{IB} 2^{-FB}$ .

- Signed range: The range of A(IB, FB) is  $-2^{IB} \le x \le 2^{IB} 2^{-FB}$ .

- Addition operands: Two binary numbers must keep the same scale in order to be added. That is, X(a, b) + Y(c, d) is only valid if X=Y (either

both A or both U) and a = c and b = d.

- Addition result: The scale of the sum of two binary numbers scaled x(a, b) is x(a+1,b), the sum of two N-bit numbers requires N+1bits.

- <u>Unsigned multiplication</u>:  $U(IB_1, FB_1) * U(IB_2, FB_2) = U(IB_1 + IB_2, FB_1 + FB_2)$ .

- Signed multiplication:  $A(IB_1, FB_1) * A(IB_2, FB_2) = U(IB_1 + IB_2 + 1, FB_1 + FB_2)$ .

## 1.4 Thesis Goal and Contributions

The investigation of fixed-point representation includes two problems: range and precision. In our research, we try to explore the two problems concurrently, and propose new methods for verifying and optimizing fixed-point circuits.

## 1.4.1 Composition of AT and Extensions

The main technique in our exploration is Arithmetic Transform (AT), which is defined in the spectral domain. The exploration of the function description in a *spectral domain* aims at elevating the classical problems with the *Boolean function domain* where a *truth table* is used. Each entry to the table describes precisely the behavior of the function at a single point, and bears no relation to the function behavior in the other points of the domain. For some applications this is satisfactory, however, other like circuit verification would benefit much more if partial information about the whole function could be included in a function value at each point of its domain. In fact, it is possible to give an alternate representation of a function where the information about the function is much more global in nature. This alternate representation is in the *spectral domain*, where a number of function properties are much more easily deduced than in the Boolean domain. However, it must be stressed that the overall information content of a given function is identical regardless of the domain considered (functional or spectral), and data in one domain can be uniquely

recreated from the data in the other. In spite of that, the meaning of the function parameters at each individual point of the two domains is dissimilar. In particular, the discrete nature of the data in the functional domain will generally be replaced by data in the spectral domain, which is global in nature, being influenced by the complete functional performance of the circuit or network under consideration. Therefore finding the spectral transform of the circuit is an important step to verification [56].

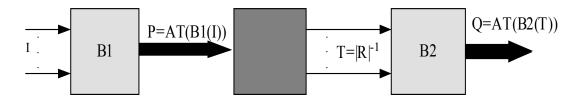

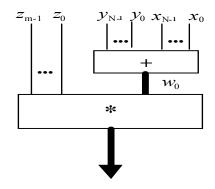

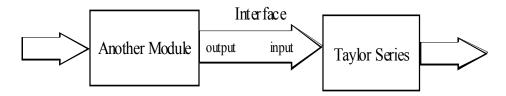

A straightforward way to compute the AT requires a multiplication with a matrix of size that is exponential in number of primary inputs. This is clearly an impractical proposition. Other methods, such as conversion from diagrams, usually focus on the whole circuit [92]. If a complex circuit comprises many smaller modules, it is hard to get its transform directly, and then the methods mentioned are invalid [94].

A complex circuit generally consists of modules such as adders, multipliers and similar, for which the transforms are easily obtained. If we can take advantage of the relatively simpler transforms to form the transform of the complex circuits, the gain would be significant. It was shown earlier [70] that AT could be composed out of transforms of circuit blocks by help of several extensions to AT, and we extend that work by constructing efficient algorithms and transform representations. In addition, since the AT representation only contains primary inputs and outputs, if engineers know the overall transform of the complex circuit in advance, compared to the compositional AT representation, they should be identical, and hence the composition procedure can perform equivalence checking. Therefore the process of constructing AT composition becomes very important. Because basic AT cannot represent sequential circuits, extensions are necessary for the purpose of the composition.

In this thesis, we explore AT and its extensions proposed by Zilic and Radecka [70] [158] then develop several subroutines to compose the detached transforms of smaller modules which exist within a bigger circuit, and finally integrate these subroutines into a fast algorithm for the construction of AT and its extensions.

## 1.4.2 Imprecise Circuits

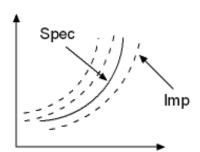

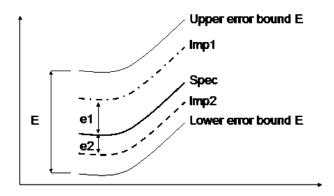

Here we focus our attention on a large category of circuits which cannot be exactly represented. We will refer to these as imprecise circuits, as implementations do not match specifications exactly since they are only realized approximately. When dealing with arithmetic circuits, the imprecision of these circuits creates added complexity for the design and verification phase. In such cases, implementations realize intended specifications only to the certain degree of precision, adding yet another dimension to the already complex process of design verification. Also it is not compulsory to require them to be identical as some imprecision reason should and could be tolerated. While verifying arithmetic circuits, if the error measured as a difference (imprecision) between them is within an acceptable range, the implementation is deemed suitable to the specification. Mathematical forms of expressing imprecision are related to the type of implemented designs. For example, for arithmetic circuits, the error can be described in some arithmetic form, and is therefore referred as an arithmetic error. Figure 1.12 denotes the basic idea of imprecise circuits. The solid line represents the specification, and the dotted lines represent the implementations. The implementations approximate the specification but not exactly overlap.

Figure 1.12: The basic idea of imprecise circuits

Mathematical forms of expressing imprecision are related to the type of implemented designs. For example, for arithmetic circuits, the error can be described in some arithmetic form, and is therefore referred as an *arithmetic error*:

The current verification methods, such as equivalence checking cannot be applied: in some cases, many output bit values may differ, while the

implementation might still be considered correct if the difference of the specification and the implementation is within a given arithmetic precision. Consider, for example, the representation of value 1.0. It is approximation 0.111... can be made arbitrarily precise by increasing the wordlength, yet all the bits are incorrect. On the other hand, the change of a single, most significant bit can change the arithmetic value by 100%.

Further, when verifying the precision, we must explore yet another problem dimension, i.e., the imprecision for the whole domain of definition. In the thesis, we address the problem by the following two aspects.

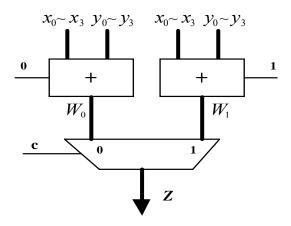

#### (A) Component Comparison

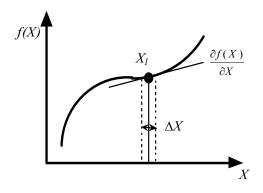

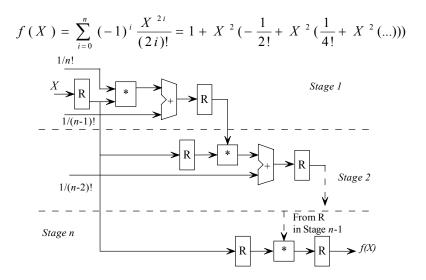

The functionality of many circuits, particularly signal processing ones, can be described or approximated by polynomials. For instance, many algorithms use a common arithmetic function such as sin(X). This function, being a real-type and infinite, cannot be realized precisely, and hence some kind of approximation is needed, like, for example, the following one:

$$X - X^3/3! + X^5/5! - X^7/7!...$$

Here *X* is within the range [-1, 1] for convergence.

In many cases the implementation of the specification function, like the above is not build from scratch. More realistic problem is to realize the function by, for example, using only 6 terms and 16-bit inputs approximation, where there is an existing module to implement sin(X) by 5 terms and 12-bit. The existing implementation can be used, as long as the difference between the requirement and the library element is not beyond the given error bound. However, to minimize the error of such a substitution, the Taylor terms and bit-width must be both optimized.

We will approach the Taylor terms and input bit-width optimization simultaneously, and try to provide a uniform platform, which is easily operated and applied. Our goal is to match and verify the precision of real DSP/arithmetic modules such as DCT. For this purpose, we present a method for matching imprecise datapath circuits expressed by Taylor series and extend it to handle word-level polynomials. Such representations are selected based on the fact that Taylor expansions provide a representation of arithmetic functions, which not only can be made arbitrarily close to the desired

(specified) function, but also give an elegant solution to the verification of imprecise designs. Therefore, we devise a flexible tool based on *Arithmetic Transforms* that can assist engineers to compute imprecision between two implementations easily.

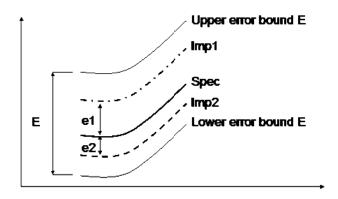

Figure 1.13 describes two components with difference. If their imprecision, that is, the maximum error, is smaller than the given error bound, the two components can be substituted by each other. This problem is solved in section 6.1.

Figure 1.13: Comparison of two implementations

#### (B) Precision Verification and Optimization

From the design perspective, however, the imprecision can provide yet another optimization resource, similar in nature to the notion of "don't cares" in logic synthesis. In particular, as implementations do not need to match specifications exactly, one can search for the least expensive implementation within the allowed imprecision.

Given an implementation with a group of parameters such as Taylor terms and input bit-width, engineers have interest to know what difference between the implementation and the specification. So we need to develop fast algorithms to compute the imprecision and verify whether the implementation fits the specification according to the given error bound.

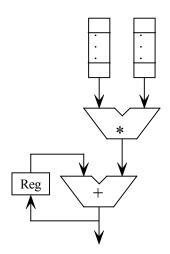

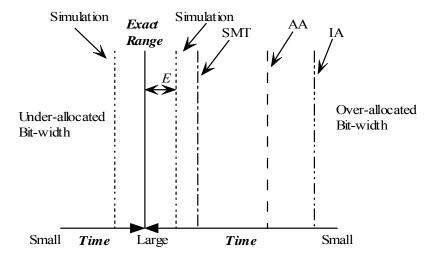

An approximate implementation is required to realize a real-valued function such as sin(X) by fixed-point circuits. Traditionally, one mostly relies on simulation-based, or *dynamic* methods, to analyze the imprecision between the specification and the implementation. In essence, one has to explore the whole

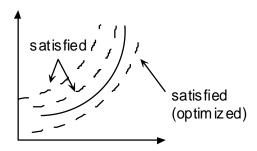

domain the function definition, with many precision parameters investigated concurrently to get the imprecision. We propose a new method in terms of Arithmetic Transform (AT) to analyze these parameters *statically*, to ascertain whether the existing implementation is suitable to the specification. Please note that many satisfying implementations can fulfill one specification, and it is very much worth finding the implementation with the smallest hardware cost. In Figure 1.14, the three dotted lines represent three implementations which all satisfy the specification represented by the solid line, but only one implementation has the smallest area. How to find out this optimized implementation is attractive in practical engineering.

Figure 1.14: Optimized implementation with the smallest area

In the thesis we try to analyze the factors generating imprecision such as function approximation and finite bit-widths, and develop a series of algorithms to process imprecise circuits included comparison, verification and optimization. This problem is solved in section 6.2 - 6.4.

## 1.4.3 Range Analysis

Range analysis is a significant step in RTL synthesis which directly influences cost and performance. This topic is always hot and attractive to engineers. Traditional methods have obvious disadvantages of low efficiency and coarse bounds, which lead to infeasibility and additional bits for data representation. In order to overcome these disadvantages, we propose a new method to calculate ranges for each intermediate output and the final output in the datapath. This method can obtain exact ranges and allocate the smallest integer bit-widths for the datapath, so the optimized implementation with the smallest hardware area can be achieved. This problem is solved in Chapter 7.

## 1.4.4 Exploration of Fixed-Point Circuits

After investigating the precision and the range separately, we explore the fixed-point representation with both integer bit-width (IB) and fractional bit-width (FB). The case is more complex and the most important problem is how to determine the fractional bit-width in the datapath and estimate the error. Based on the above analysis, we propose an efficient method to allocate appropriate IB and FB for the inputs and all outputs in the datapath in order to obtain the optimized implementation.

As blind spots in past explorations, circuits with feedbacks – such as IIR filters – are of importance. We analyze feedback circuits and propose algorithms to detect stability and find ranges. Furthermore, sequential circuits are investigated and the process of fixed-point representation is extended to floating-point representation. These problems are solved in Chapter 8.

#### 1.4.5 Contributions

On the whole, the main contributions of the thesis are in:

- designing an algorithm to obtain the spectral transform for a complex circuit

- proposing algorithms to verify and optimized imprecise circuits

- proposing an algorithm to calculate ranges of a datapath

- conceiving an algorithm to find the optimized fixed-point implementation with integer and fractional bit-widths

- designing an algorithm to explore imprecise arithmetic circuits with feedback.

# Chapter 2

# **Background**

In this chapter, we review function representations including truth tables, Shanon expansion and polynomial representation. We pay special tribune to decision diagrams, as they play an important role in many classical verification methods. Most commonly used diagrams include OBDDs, MTBDDs, BMDs and TEDs. Finally, as usual methods to handle imprecise circuits rely on dynamic analysis and affine arithmetic, we conclude this chapter with the introduction of the mathematical background of these methods.

With VLSI (Very Large Scale Integration) technologies and the design techniques developing rapidly, microchips are utilized prevalently in many areas of human activities. The integration density increases fast beyond billions of transistors bringing forward a problem: how to build a right system to fit requirements? Thus hardware verification theory emerges as an important element of the overall design process. There were many corresponding explorations in past decades. In this chapter we will review some typical theoretical background dealing with function representations and verification.

# 2.1 Function Representations

Digital combinational circuits rely on the repreentation of *Boolean functions*, either by means of *computation* or *evaluation processes*. *Truth tables* belong to the first group, while *decision diagrams* belong to the second one.

#### 2.1.1 Truth Table

A *truth table* is a mathematical table used in logic — specifically in connection with Boolean algebra, Boolean functions, and propositional calculus — to compute the functional values of logical expressions on each of their functional arguments, that is, on each combination of values taken by their logical (input) variables. In particular, truth tables can be used to tell whether a propositional expression is true for all legitimate input values, that is, logically valid.

**Example 2.1:** The truth table of the 2-bit unsigned adder with inputs  $x = x_1x_0$  and  $y = y_1y_0$ , and output  $z = z_2z_1z_0$  is presented below.

| $x_1x_0y_1y_0$ | $z_2z_1z_0$ |

|----------------|-------------|

| $0\ 0\ 0\ 0$   | $0 \ 0 \ 0$ |

| 0001           | 001         |

| 0010           | 010         |

| 0011           | 0 1 1       |

Truth tables are useful in many synthesis applications, as well, as verification due to their canonical property. In fact, equivalence checking of two Boolean functions can be done by comparing truth tables of corresponding functions.

A truth table has  $2^N$  rows for an N-input function, hence the size and time complexity are always exponential in the number of primary inputs. Consequently, the truth table as a binary function representation is impratical for verification of even moderate size circuits.

## 2.1.2 Shannon Expansion

In mathematics, Shannon expansion is a method by which a Boolean function can be represented by the sum of two sub-functions (co-factors) of the original. It provides a way for deriving a Boolean function recursively.

**Definition 2.1:** The cofactor of a Boolean function  $f(x_0, x_2, ..., x_i, ..., x_{n-1})$  with respect to variable  $x_i$  is  $f_{x_i} = f(x_0, x_1, ..., 1, ..., x_{n-1})$ . Similarly, the cofactor with respect to variable  $\overline{x_i}$  is  $f_{\overline{x_i}} = f(x_0, x_1, ..., 0, ..., x_{n-1})$ .

Each Boolean function can be represented by its cofactors through Shannon expansion.

**Theorem 2.1:** A Boolean function

$$f: B^n \to B$$

can be represented as

$$f_{x_i} = f(x_1, x_2, ..., x_i, x_n) = x_i \cdot f_{x_i} + \overline{x_i} \cdot f_{\overline{x_i}} = (x_i + f_{\overline{x_i}}) \cdot (\overline{x_i} + f_{x_i})$$

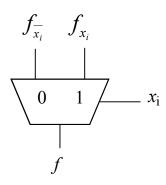

One way of representing the Shannon's expansion is by means of a multiplexer selects between the two cofactors, depending on the value of a splitting variable  $x_i$ .

Figure 2.1: Shannon expansion in variable  $x_i$

**Example 2.2:** Given a function of f = xyz + xy'z + x'y'z + x'y'z', we can re-write the function in terms of any two variables — namely, a variable and its complement:  $f = xg_x + x'g'_x$ . Simply apply the distributive theorem to the function about x: f = x'(y'z + y'z' + yz) + x(yz + y'z). Now we have expanded the function f about the variable x. The work [154] describes a method based on Shannon expansion for low-power and testable circuit synthesis.

# 2.1.3 Polynomial Representation

Positive and negative Davio expansions are other two expressions of Boolean functions by means of cofactors and the XOR operation.

**Definition 2.2:** The positive Davio expansion of a Boolean function  $f(x_0, x_2, ..., x_i, ..., x_{n-1})$  with respect to variable  $x_i$  is:

$$f = f(x_0, x_1, ..., x_i, ... x_{n-1}) = f_{\overline{x_i}} \oplus x_i \cdot (f_{\overline{x_i}} \oplus f_{x_i})$$

Similarly, the begative Davio expansion is:

$$f = f(x_0, x_1, ..., x_i, ..., x_{n-1}) = f_{x_i} \oplus \overline{x_i} \cdot (f_{\overline{x_i}} \oplus f_{x_i})$$

The two representations adopt XOR operations over two cofactors. They are useful for polynomial expressions and decision diagrams representations.

If all variables are decomposed by positive Davio expansion, another canonical representation of Boolean functions is obtained as Reed-Muller transform [4], [5], [6]. RM transform is used in technology mapping by symmetry detection, which will be introduced in section 3.1.2.

### 2.1.4 Boolean Satisfiability

Boolean Satisfiability (SAT) is often used as the underlying model for a significant and increasing number of applications in electronic design automation (EDA) as well as in many other fields of computer science and engineering. Satisfiability determines whether the variables of a given Boolean formula can be assigned in such a way as to make the formula evaluate to TRUE. Another importance is to determine whether no presence of such assignments would imply that the function expressed by the formula is identically FALSE for all possible variable assignments. In this latter case, we say that the function is unsatisfiable, or else it is satisfiable [152].

The SAT is a decision problem in complexity theory, whose instance is a Boolean expression written using operations of AND, OR, NOT, variables, and parentheses. The question is that given the expression, whether some assignment of *TRUE* and *FALSE* values to the variables will make the entire expression true. In particular, satisfiability searches are most often applied to Boolean functions represented as product of sums. The search for a function variables assignment, which would make all the clauses true, is proven to be NP-Complete [152].

**Example 2.3:** After converting Boolean equations from Example 2.1 into product-of-sums, we obtain the following set of clauses:

$$f(x_1, x_0, y_1, y_0) = \begin{bmatrix} z_2 \\ z_1 \\ z_0 \end{bmatrix} = \begin{bmatrix} (x_1 + x_0)(y_1 + y_0)(x_1 + y_1)(x_1 + y_0)(x_0 + y_1) \\ (x_1 + y_1 + y_0)(x_1 + x_0 + y_1)(\overline{x}_1 + \overline{y}_1 + y_0)(\overline{x}_1 + x_0 + \overline{y}_1)(\overline{x}_1 + \overline{x}_0 + y_1 + \overline{y}_0)(x_1 + \overline{x}_0 + \overline{y}_1 + \overline{y}_0) \\ (x_0 + y_0)(\overline{x}_0 + \overline{y}_0) \end{bmatrix}$$

The set of input assignments satisfying the above equations is empty. This fact is easy to verify by checking the multiplier truth table, which holds no input  $(x_1, x_0, y_1, y_0)$  assignment resulting in all the output bits  $(z_2, z_1, z_0)$  being equal to one.

# 2.2 Decision Diagrams

Decision diagrams are the binary function representations that explore evaluation process. They do not need to compute the response of input stimuli and evaluate a function based on a set of binary-valued decisions.

## 2.2.1 Binary Decision Diagrams

Binary decision diagram (BDD) [7] was already introduced in 1959 as a data structure that is used to represent a Boolean function. Furthermore, under the name of Branching Programs they were intensively studied in theoretical computer science. Within the following years the importance of BDDs for VLSI CAD was realized by several groups, and an increasing number of BDD algorithms and successful applications were reported.

On a more abstract level, BDDs can be considered as a compressed representation of sets or relations. Unlike other compressed representations, operations are performed directly on the compressed representation, i.e. without decompression. BDDs are based on the Shannon expansion. Generally, bit-level decision diagrams are constructed in terms of one of the three Boolean function decompositions:

Shannon:

$$f = \overline{x_i} \cdot f_{\overline{x_i}} \oplus x_i \cdot f_{x_i}$$

positive Davio:  $f = f_{\overline{x_i}} \oplus x_i \cdot (f_{x_i} \oplus f_{\overline{x_i}})$

negative Davio:  $f = f_{x_i} \oplus \overline{x_i} \cdot (f_{x_i} \oplus f_{\overline{x_i}})$

**Definition 2.3:** "A Decision Diagram (DD) over a set of Boolean variables  $X_n$  and a non-empty terminal set T is a connected, directed acyclic graph G=(V, E) with exactly one root and the following properties:

- $\blacksquare$  A vertex in V is either a non-terminal or a terminal vertex.

- Each non-terminal vertex v is labeled with a variable from  $X_n$ , called the index index(v) of v and has exactly two successors in V, denoted by low(v), high(v).

- Each terminal vertex v is labeled with a value  $value(v) \in T$  and has no successors." [7]

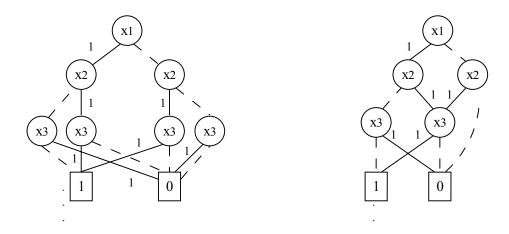

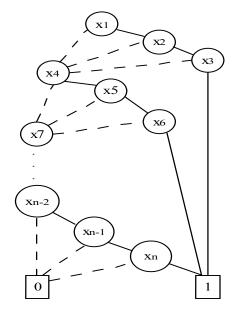

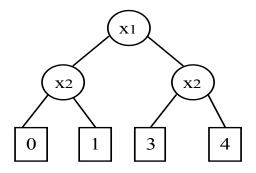

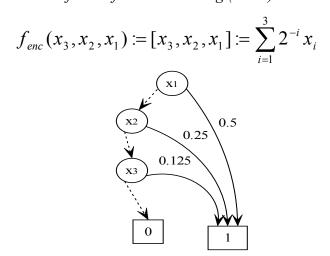

**Example 2.4:** Consider Decision Diagrams in Figure 2.2 and 2.3. The graph in Figure 2.2 represents a complete tree that by definition is also a complete and ordered DD. The DD in Figure 2.3 is also ordered, but not complete. Since both DDs are ordered they are also free.

Figure 2.2: Complete and ordered DD

Figure 2.3: Ordered DD

**Definition 2.4:** "A BDD is a DD over  $X_n$  and terminal set  $T = \{0, 1\}$ . If the BDD has a root vertex v, then the BDD represents a Boolean function  $f_v$  defined as follows:

- 1. If v is a terminal vertex and value(v)=1 (value(v)=0), then  $f_v=1$  ( $f_v=0$ ).

- 2. If v is a non-terminal vertex and index(v) =  $x_i$ , then  $f_v$  is the function

$$f_{\nu}(x_{1},...,x_{n}) = \overline{x_{i}} \cdot f_{low(\nu)}(x_{1},...,x_{n}) + x_{i} \cdot f_{high(\nu)}(x_{1},...,x_{n}).$$

$f_{low(v)}(f_{high(v)})$  denotes the function represented by low(v) (high(v))." [7]

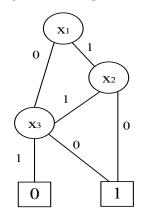

# 2.2.2 Reduced Ordered Binary Decision Diagrams

BDDs have obvious limitations because of exponential sizes which confine

applications. Some extensions have been proposed to overcome these limitations. Recently, (especially in the area of verification) DDs have also been used to represent Pseudo-Boolean functions, i.e., function of the form  $f: B^n \to Z$ . The simplest extension of BDDs, ROBDDs (Reduced Ordered Binary Decision Diagrams), has two restrictions:

- Appearance of the variable keeps in the same order along each path from the root to a terminal.

- No isomorphic sub-trees or redundant vertices exist.

**Definition: 2.5:** "Let  $\pi$  be a total order on the set of variables  $x_1,...x_n$ . An ordered binary decision diagram (OBDD) with respect to the variable order  $\pi$  is a directed acyclic graph with exactly one root which satisfies the following properties:

- There are exactly two nodes without outgoing edges. These two nodes are labeled by the constants 1 and 0, respectively, and are called sinks.

- Each non-sink node is labeled by a variable  $x_i$ , and has two outgoing edges, which are labeled by 1 and 0, respectively. These edges are called the 1-edge and the 0-edge, respectively.

- The order, in which the variable appear on a path in the graph, is consistent with the variable order  $\pi$ , i.e., for each edge leading from a node labeled by  $x_i$  to a node labeled by  $x_j$  it holds  $x_i <_{\pi} x_j$ ." [7]

An OBDD is a read-once branching program with an additional ordering restriction on the variables. The computation path of an input  $a = (a_1, ..., a_n) \in B^n$  is the path from the root to a sink in the OBDD which is defined by the input. More precisely, the computation path begins in the root, and in each node labeled by  $x_i$  the path follows the edge with label  $a_i$ .

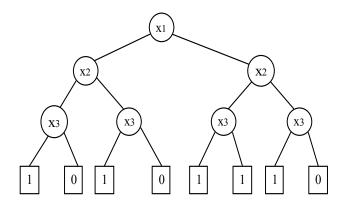

**Example 2.5:** Let  $\pi$  be the variable order  $x_1 < x_2 < x_3$ . Figure 2.4 illustrates two OBDD representations of the function  $f(x_1, x_2, x_3) = x_1x_2 + \overline{x_3}x_1\overline{x_2}$  with respect to the order  $\pi$ .

Figure 2.4: Two OBDDs of Example 2.5